JAJSTU7H August 2007 – July 2024 CDCE937 , CDCEL937

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

9.2.3 Application Curves

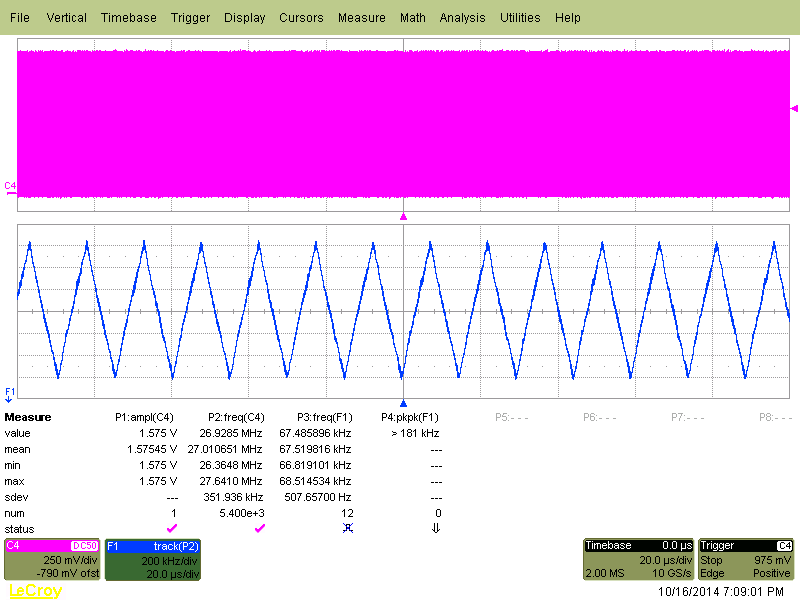

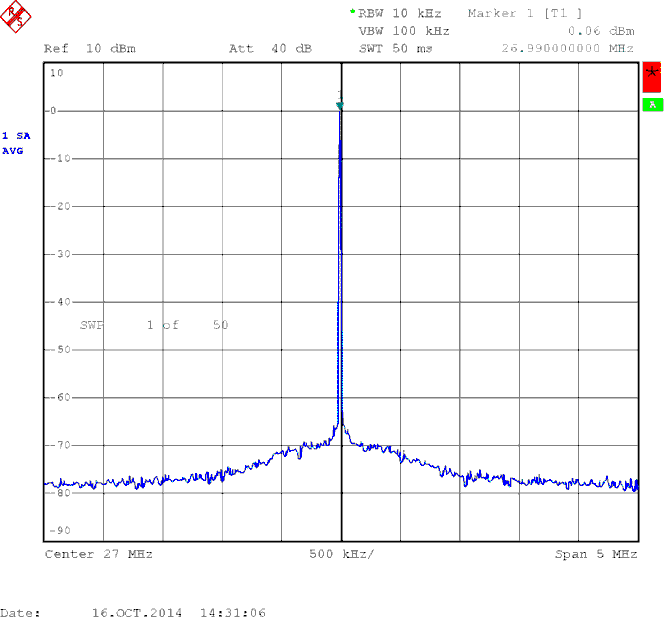

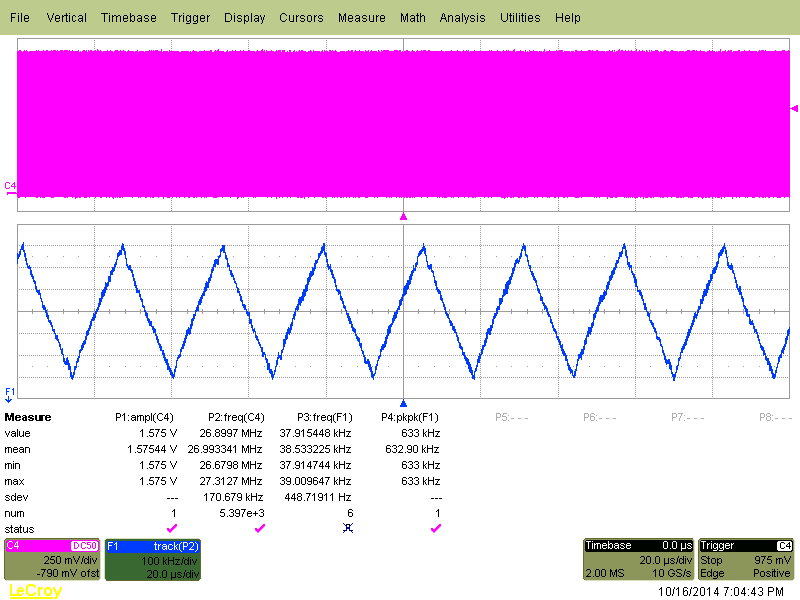

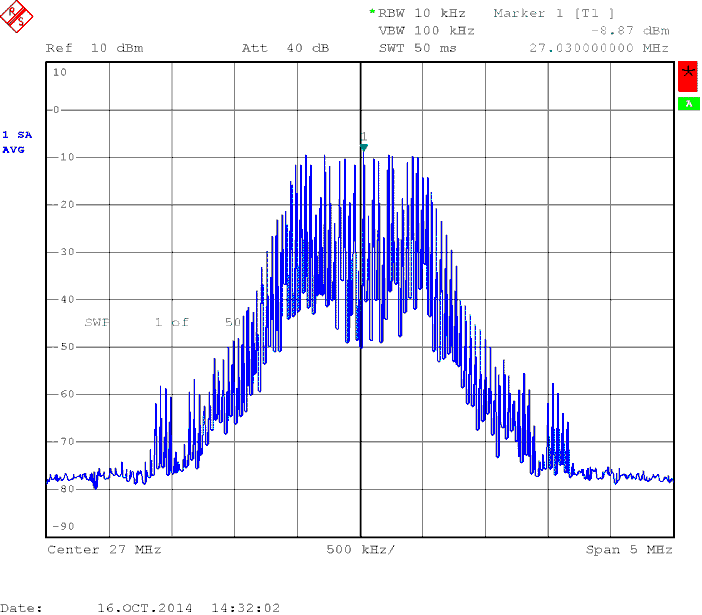

Figure 9-6, Figure 9-7, Figure 9-8, and Figure 9-9 show CDCEx937 measurements with the SSC feature enabled. Device configuration: 27-MHz input, 27-MHz output.

Figure 9-6 fout = 27 MHz, VCO frequency < 125 MHz, SSC (2% center)

Figure 9-6 fout = 27 MHz, VCO frequency < 125 MHz, SSC (2% center) Figure 9-8 Output Spectrum With SSC Off

Figure 9-8 Output Spectrum With SSC Off Figure 9-7 fout = 27 MHz, VCO frequency > 175 MHz, SSC (1%, center)

Figure 9-7 fout = 27 MHz, VCO frequency > 175 MHz, SSC (1%, center) Figure 9-9 Output Spectrum With SSC On, 2% Center

Figure 9-9 Output Spectrum With SSC On, 2% Center