JAJT297 June 2019 LM5155 , LM51551 , LM5156

昇圧コンバータは、低い入力電圧を高い出力電圧に変換します。昇圧比をできる限り高くするには、動作デューティ サイクルを最大化する必要があります。

昇圧コントローラには最大連続デューティ サイクルに制限があり、一般的には低いスイッチング周波数で最大になります。この最大デューティ サイクルを超えると、パルス スキップが発生します。通常これは悪影響をもたらすため、回避する必要があります。多くのコントローラの最大デューティ サイクルは 80%〜90% の範囲で、非常に低いスイッチング周波数で動作している場合は数パーセント高くなる可能性があります。スイッチング周波数を低くするには、部品を大きくし、回路基板の面積を増やす必要があります。ただし、低いスイッチング周波数で動作しているときでも、十分な昇圧が得られない場合があります。この問題を解決するにはどうすればよいでしょうか。

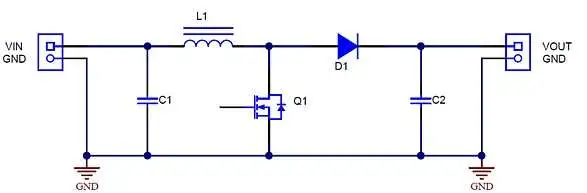

図 1 に、従来型の昇圧コンバータ電力段の概略回路図を示します。この構成の主な利点は、部品数が少なく、標準的なインダクタを搭載しており、シンプルなローサイド昇圧コントローラを実装できることです。ただし、この基本的な昇圧の主な制限は、最大デューティ サイクルが 90% であるとした場合、最大昇圧比は 10 : 1 に限定されることです。これを超える昇圧が必要な場合は、フライバック コンバータ、または昇圧コンバータとチャージ ポンプ ダブラーを使用できます。昇圧コンバータにチャージ ポンプを追加することは、低出力電流には適していますが、実装に追加の部品が必要になります。フライバックも妥当なソリューションです。ただし、トランス ピン数が少なくて巻線比が低く、漏れインダクタンスの小さいよりシンプルなソリューションも存在します。

図 1 従来型の単一インダクタ昇圧コンバータ電力段

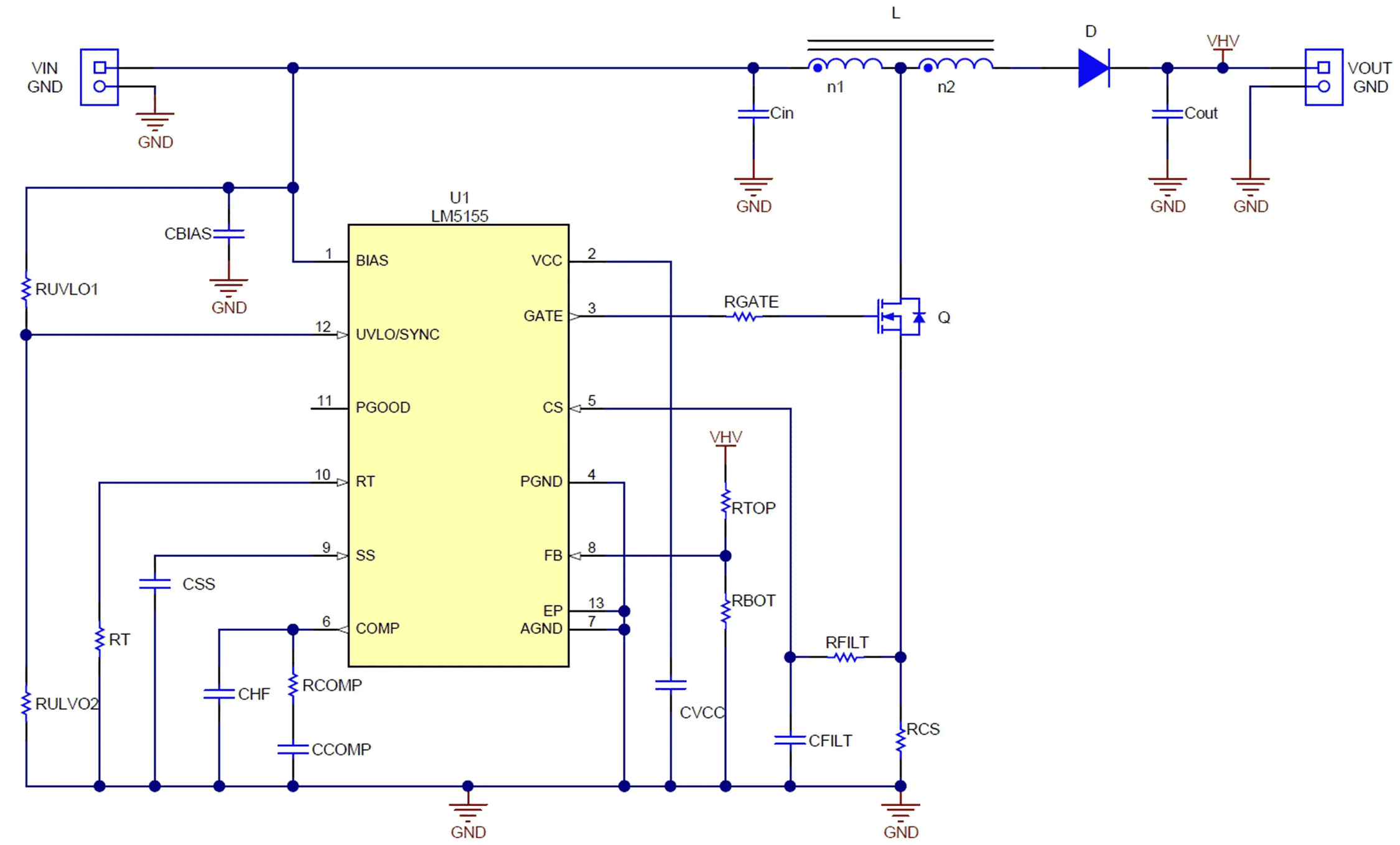

図 1 従来型の単一インダクタ昇圧コンバータ電力段図 2 に、オートトランス昇圧コンバータを示します。同じコア上で 2 つの直列接続された巻線が使用され、これが絶縁なしのトランスとして動作します。1 次側を 2 次側と直列に配置すると、フライバックと比較して必要な巻線比が低くなり、必要なピン数も少なくてすみます。

図 2 オートトランス昇圧コンバータは、従来の昇圧コンバータよりも高い出力電圧を供給

図 2 オートトランス昇圧コンバータは、従来の昇圧コンバータよりも高い出力電圧を供給式 1 は、特定の Vin、Vout、巻線比 n2/n1 における、連続導通モード (CCM) でのデューティ サイクルを表します (電界効果トランジスタ [FET] と電流検出抵抗による電圧降下は無視)。

巻線比 n2/n1 が大きくなると、デューティ サイクルが減少することがわかります。これは、より高い出力電圧を供給する場合に有益です。この式を Vout を求める式に変換すると、式 2 が得られます。

n2/n1 = 0 の場合、この式は従来型の昇圧コンバータの式と同じになります。巻線比 n2/n1 がゼロでない場合、Vout は (n2/n1)*Vin*d/(1-d) だけ増加するため、はるかに高い出力電圧を実現できます。

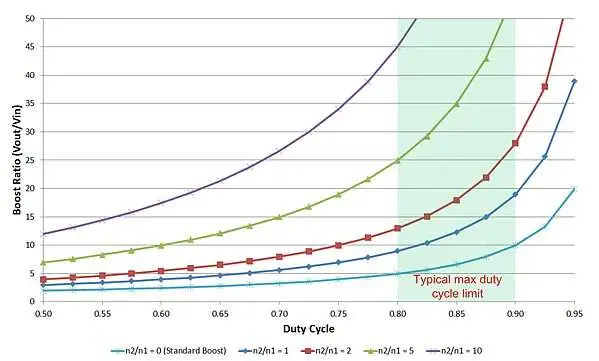

図 3 に、いくつかの巻線比 n2/n1 について、昇圧比 Vout/Vin とデューティ サイクルとの関係を示します。比較のため、従来型の昇圧の巻線比がゼロの場合も含めています。デューティ サイクルが 90% の場合、従来型の昇圧回路では昇圧比が 10 であるのに対し、n2/n1 = 1 では 19 となり、出力電圧が 2 倍近くになります。入手が容易な標準の結合型インダクタを使用して、1:1 の n2/n1 の比を簡単に実装できます。巻線比を大きくすると、出力電圧は大幅に高くなります。

図 3 タップ付きインダクタは低いデューティ サイクルでより高い出力電圧を実現

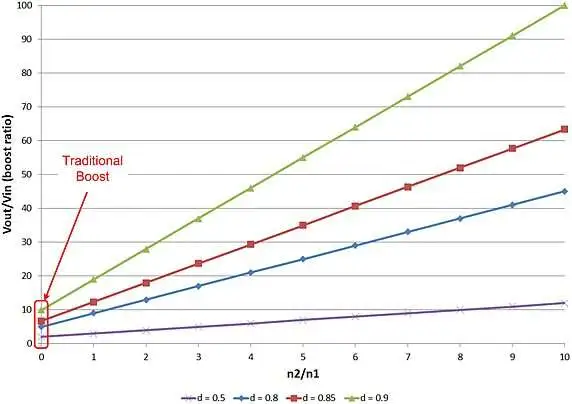

図 3 タップ付きインダクタは低いデューティ サイクルでより高い出力電圧を実現通常は、設計の仕様から昇圧比を決定できます。実用的な最大デューティ サイクルは、選択したコントローラと必要なスイッチング周波数によって決まります。図 4 に、必要な巻線比を簡単に決定する方法を示します。たとえば、10V の入力から 250V の出力を得る必要があり、最大デューティ サイクルを 80% に制限するとします。青い曲線 (d=0.8) をたどって 250V/10V = 25 の昇圧比を得るのに必要な n2/n1 を調べると、5 であることがわかります。

式 3 はオフ時の FET の電圧ストレス、式 4 は整流器の逆電圧ストレスを表します。

上記の設計例では、FET と整流器の電圧ストレスはそれぞれ 50V と 300V です。FET の電圧ストレスは、両端に約 250V の電圧が印加される従来の昇圧回路よりもかなり低くなります。漏れインダクタンスが存在するため、リンギングを低減するために抵抗とコンデンサで構成されたスナバが必要になることがあります。

図 4 昇圧比と最大デューティ サイクルを選択して必要な巻線比を決定

図 4 昇圧比と最大デューティ サイクルを選択して必要な巻線比を決定CCM 昇圧コンバータにオートトランスを実装すると、いくつかの利点があります。巻線を追加するだけで、従来の昇圧コンバータを上回る出力電圧を得られます。動作デューティ サイクルが低減されるため、スイッチング周波数を高くでき、部品サイズの小型化と FET 電圧の低減を実現できます。デューティ サイクルを低減すると、従来の昇圧コンバータに実装した場合には十分に高いデューティ サイクルで動作できないコントローラを使用できるようになり、選択肢が広がる可能性もあります。

その他の Power Tips については、Power House でテキサス・インスツルメンツの Power Tips ブログ シリーズをご覧ください。