-

試験 / 測定アプリケーションにおける RF サンプリング データ コンバータの高速周波数ホッピングに関する考察

1 はじめに

データ コンバータが進化し続ける中で、ソフトウェア無線、ワイヤレス テスタ、スペクトラム アナライザのようなシステムでマルチバンド要件を満たすことが課題となっています。デバイスがますます複雑になり、数値制御発振器 (NCO) 周波数間の遷移が高速になっているため、システム設計者は従来の周波数ホッピング方式を再評価しています。

この記事では、周波数ホッピング手法の進化について説明し、汎用入出力 (GPIO) や高速再構成インターフェイス (FRI) など、従来の手法と高度な手法を比較します。これらの進歩を理解することで、シングルバンドとマルチバンド両方のアプリケーションにおいて周波数ホッピングを最適化するために有益な情報を得ることができます。最新のシステムがマルチバンド要件をどのように満たしているかを十分に理解するには、まず周波数ホッピングの基礎を理解することが不可欠です。

2 周波数ホッピングとは

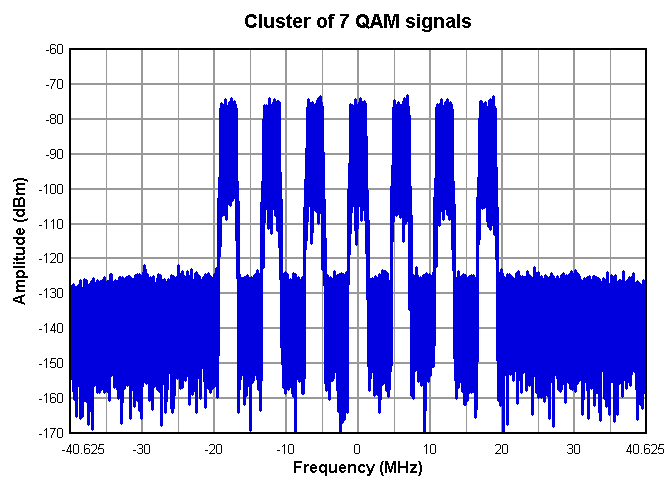

Wi-Fi® 6 と 7、または直交振幅変調 (QAM) エンコード信号などの最新の通信システムでは、スペクトルは本質的にマルチバンドです。つまり、無線周波数 (RF) ドメインは各周波数帯域内の複数のチャネルで構成されます。たとえば、Wi-Fi 6 と Wi-Fi 7 は同じ周波数帯域内の複数のチャネルで動作し、帯域幅とデータ スループットを動的に最大化します。一方、QAM では、データを 1 つのチャネル内の異なる位相オフセットと振幅レベルにエンコードする必要があります。図 1 に、7 つの QAM チャネルを含む周波数帯域の例を示します。

図 1 周波数ドメインのマルチトーン信号。

図 1 周波数ドメインのマルチトーン信号。直接 RF サンプリング A/D コンバータ (ADC) と D/A コンバータ (DAC) には、多くのデジタル機能が組み込まれています。直接 RF サンプリングを可能にする最も重要な機能の 1 つは、ADC 内のデジタル ダウンコンバータ (DDC) と、DAC 内のデジタル アップコンバータ (DUC) です。

ADC 内の DDC は、NCO、デジタル ミキサ、デシメータ ブロックの 3 つの主なコンポーネントで構成されています。NCO は、従来型のレシーバ信号チェーンでは局部発振器のデジタル版として機能し、入力信号と混合することでベースバンド (ナイキスト ゾーン 1) 内の信号を供給しますが、これには望ましくない影像が含まれます。デシメータ ブロックは、有限インパルス応答 (FIR) デシメーション フィルタを介してこれらの影像をフィルタ処理してから、ダウンサンプリングすることにより信号帯域幅を低減します。デシメータ ブロックは、中間周波数 (IF) フィルタのデジタル等価です。

DAC 内の DUC は、補間器、NCO、およびデジタル ミキサで構成されます。補間器は、ADC とは異なり、低帯域幅の入力信号をアップサンプリングし、 FIR フィルタを介して影像を抑制します。補間段の後、出力信号はデジタル ミキサに送信されて NCO と混合されるため、DAC はより低い入力信号帯域幅で広いナイキスト ゾーンにわたって動作できます。

RF サンプリング コンバータの特定の入力でアクティブな DDC の数によって、コンバータがシングルバンド出力またはマルチバンド出力のどちらで動作するのかが決まります。この記事では、周波数ホッピングの ADC の側面に注目します。

図 2 に、3GSPS でデュアル チャネル、クワッド バンド動作可能な RF サンプリング ADC であるテキサス・インスツルメンツの ADC32RF55 からの DDC の例を示します。

図 2 ADC32RF55 の機能ブロック図 (チャネルごとに 4 つの DDC)。

図 2 ADC32RF55 の機能ブロック図 (チャネルごとに 4 つの DDC)。多くの場合、対象となる周波数帯域が変更される可能性があります。帯域ごとに完全に独自のシグナル チェーンに切り替える代わりに、同じ RF サンプリング コンバータを使用して、新しい周波数帯域に合わせて NCO 周波数を調整できます。これは、最新の RF サンプリング コンバータの大きな利点です。NCO をある周波数から別の周波数に変更する操作を周波数ホッピングと呼びます。

NCO はアナログ周波数を直接生成するのではなく、目的の周波数の高分解能デジタル表現を生成します。各 NCO はデジタル ワード (通常は 48 ビット以上) を受信します。このワードを NCO 位相アキュムレータと組み合わせることで、デジタル ミキシング段に適した信号を表現できます。NCO をプログラムする際は、実際の周波数ではなく、目的の IF に対応するデジタル表現をプログラムします。最も一般的にサポートされる NCO 周波数範囲は、-Fs/2〜Fs/2 です (Fs はコンバータのサンプリング周波数)。負の周波数ワードが偶数ナイキスト ゾーンに使用され、正の周波数ワードが奇数ナイキスト ゾーンの信号に使用されます。

高次 NCO 周波数がベースバンドのどこに現れるかを判断するための最初のタスクは、目的の周波数とサンプル レートの間でモジュラス演算を実行し、 Fs の倍数を除去することです。これで、目的の NCO 周波数が 0Hz とコンバータのサンプル レート Fs の間になります。

NCO 周波数がナイキスト周波数 (Fs/2) より小さい場合、式 1 に示すように、目的の NCO 周波数は奇数ナイキスト ゾーンに変換されます。

計算された NCO 周波数がナイキスト周波数を上回っている場合、式 2 に示すように、周波数は偶数ナイキスト ゾーン内になります。

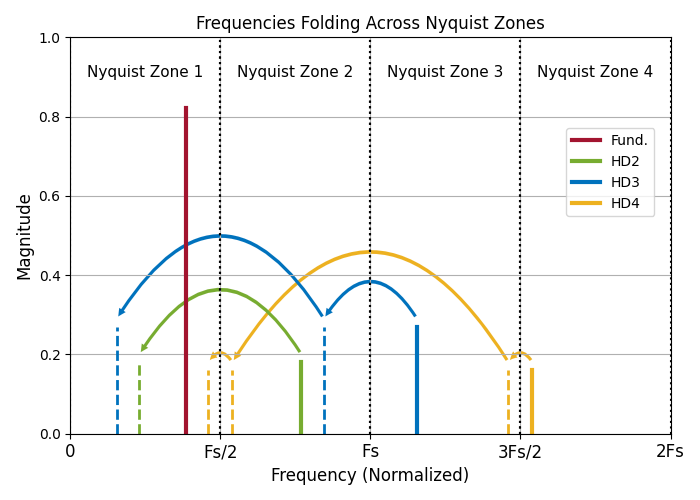

図 3 に、基本信号 (Fund.) とその 2 次、 3 次、 4 次の高調波 (HD2、HD3、HD4) が、実際には高次ナイキスト ゾーン内であるのにもかかわらず、最初のナイキスト ゾーンに折り返される様子を示します。

図 3 高次ナイキスト ゾーンからナイキスト ゾーン 1 に折り返された高調波。

図 3 高次ナイキスト ゾーンからナイキスト ゾーン 1 に折り返された高調波。従来の ADC と比較した RF サンプリング ADC の利点の 1 つは、周波数帯域を切り替えるためにハードウェアを変更する必要がないことです。RF サンプリング ADC にはこの固有の柔軟性があるため、追加のハードウェア部品を必要とせずに新しい周波数帯域に迅速に適応でき、システム設計を簡素化してコストを削減できます。ただし、このプロセスは瞬間的なものではありません。RF サンプリング ADC の初期の設計では、各 NCO と後続の DDC で使用できる NCO ワード オプションは 1 つのみでした。そのため、別の周波数へのホッピングには複数のレジスタ書き込み操作が必要でした。

新しい NCO ワードは、シリアル ペリフェラル インターフェイス (SPI) を介して書き込まれた後、もう一度レジスタ書き込みを行って、新しい NCO ワードを DDC ブロックにプッシュして、実際に有効化する必要があります。周波数ホッピングに必要な時間には、NCO ワードの長さや SPI トランザクション速度など、いくつかの要因が影響します。多くの場合、ADC のレジスタ サイズは 8 ビットに制限されているため、48 ビット NCO を更新するには合計 7 つのレジスタ書き込み (NCO ワード自体に対する 6 つのレジスタ書き込みと、DDC を更新するための追加のレジスタ書き込み) が必要です。

各 SPI トランザクション (通常は各レジスタ書き込みに対して 16 ビットのアドレス) のオーバーヘッドを考慮すると、トランザクション時間は 3 倍になります。シリアル クロック信号 (SCLK) レートが 20MHz の場合、SPI データがノンストップ ストリームであれば、式 3 で周波数ホッピングの時間を計算できます。

3 周波数ホッピング手法の進化

現在、RF コンバータは DDC ごとに複数の NCO ワードで設計されており、NCO ワードの事前プログラミングが可能です。この革新的なアプローチでは、コンバータのメモリに複数の周波数値をプリロードすることで、より高速な周波数ホッピングを実現できます。高速周波数ホッピングの「高速」は、事前に計算された NCO ワードを格納するこの概念から来ています。

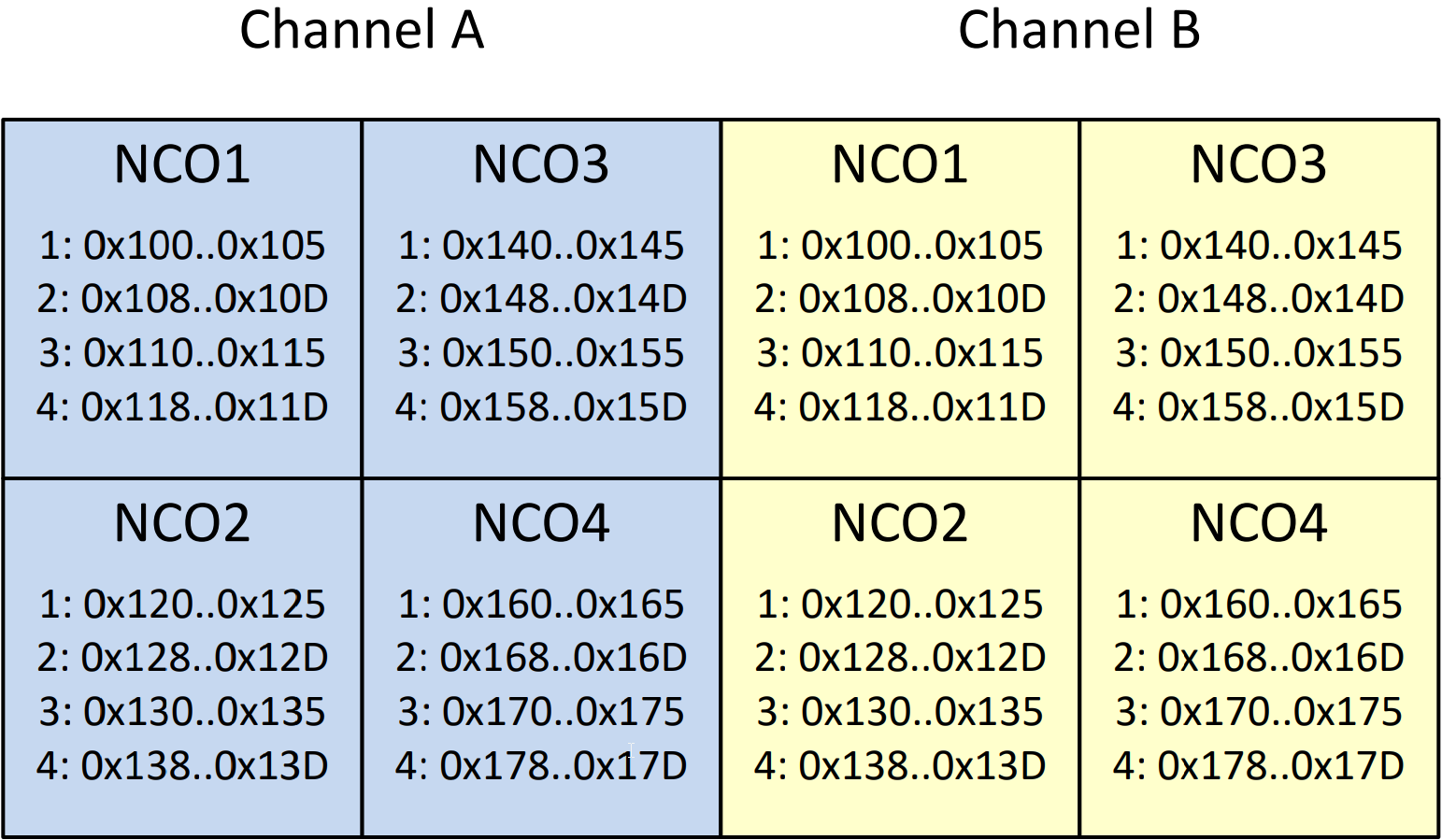

図 4に、ADC32RF55 の 48 ビット NCO レジスタ アドレスを NCO インデックスおよびワード インデックス別に示します。このデバイスにはレジスタ マップ ページングが実装されており、読み取りおよび書き込み操作からアクティブ ページに含まれていないレジスタをマスクできるため、チャネル A とチャネル B のアドレスは同じですが、周波数ワードは一意です。

図 4 ADC32RF55 のチャネル別および NCO インデックス別の NCO ワード アドレス。

図 4 ADC32RF55 のチャネル別および NCO インデックス別の NCO ワード アドレス。ワードがプログラムされた後、どのように特定のワードを選択するのでしょうか。NCO ワードを変更するには、DDC 用に新しい NCO ワードを選択する必要があります。これには、SPI ピンまたは GPIO ピンを使用できます。表 1 に、アクティブな帯域数に応じて、ADC32RF55 で指定された DDC 用に個別のワードを選択する方法の例を示します。標準構成では、この ADC は DDC ごとに 4 つの一意の NCO ワードを備えていますが、シングルバンド モードでは、隣接する DDC の 4 つの NCO ワードからアクティブ NCO に供給することもできます。つまり、各チャネルの DDC は、事前にプログラムされた 8 つの NCO ワードにアクセスできます。

| 帯域の数 | ADDR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|---|---|

| シングル | 0x3B | 0 | 0 | 0 | 0 | NCO2 CHA[1:0] | 0 | NCO1 CHA[1:0] | |

| 0x41 | 0 | 0 | 0 | 0 | NCO2 CHB[1:0] | 0 | NCO1 CHB[1:0] | ||

| デュアル | 0x3B | 0 | 0 | 0 | 0 | NCO2 CHA[1:0] | NCO1 CHA[1:0] | ||

| 0x41 | 0 | 0 | 0 | 0 | NCO2 CHB[1:0] | NCO1 CHB[1:0] | |||

| クワッド | 0x3B | NCO4 CHA[1:0] | NCO3 CHA[1:0] | NCO2 CHA[1:0] | NCO1 CHA[1:0] | ||||

| 0x41 | NCO4 CHB[1:0] | NCO3 CHB[1:0] | NCO2 CHB[1:0] | NCO1 CHB[1:0] | |||||

周波数ホッピングの実行に必要な時間は、コンバータによって異なります。一般的には、SPI 方式に必要な時間は、式 3 に示すように、7 回ではなく 1 回の SPI トランザクションの時間のみです。SPI 方式の速度は、SPI の最大クロック レートとシリアル データ転送に伴うオーバーヘッドによってさらに制限されます。式 4 に、同じ 20MHz SCLK を想定した場合にデバイスが NCO ワードの変更を開始するまでに必要な時間を示します。

これに対して、GPIO 方式は GPIO 入力の更新と同じ速度で実行できます。電圧がその High レベルまたは Low レベルのスレッショルドを超えると、NCO ワードの変更変化が開始します。

どちらの方法でも、デバイスが NCO ワードの変更を受信すると、内部 NCO ワードは即座に更新されます。ただし、デシメーション フィルタがすべての古い値をフラッシュする必要があるため、デシメーション係数に応じた若干の遅延が発生します。

表 2に 、ADC32RF55 でデシメーション フィルタを新しい NCO 周波数と混合したデータでフラッシュするために必要な時間を示します。

| デシメーション設定 | NCO スイッチング時間 |

|---|---|

| /4 | 約 250ns |

| /8 | 約 350ns |

| /16 | 約 600ns |

| /32 | 約 1μs |

| /64 | 約 2μs |

| /128 | 約 4μs |

一般的に、周波数ホッピングは GPIO 方式の方が SPI 方式よりも高速です。これは、GPIO インターフェイスは本質的に並列であるためです。ただし、考慮事項が 1 つあります。GPIO ワード選択モードでは、アクティブなすべての DDC に同じワード インデックスが適用されます。DDC2 でワード 3 を使用している間、DDC1 でワード 1 を使用することはできません。GPIO インターフェイスは、すべての DDC を同じワード インデックスに設定します。

もう 1 つの方法である FRI では、特定のデバイス ピンを使用して、標準 SPI でサポートされている速度よりもはるかに高速なレートでデータを送信します。テキサス・インスツルメンツの DAC39RF12 のような一部のデバイスは、200MHz までの FRI 通信をサポートしており、アクティブな NCO ワードの選択に使用できます。

4 試験 / 測定機器分野のアプリケーション

試験 / 測定機器では、さまざまなアプリケーションのニーズが多様化し、進化しているため、複数の周波数帯域のサポートは不可欠です。広帯域試験装置は、複数の周波数範囲にわたって動作できるため、さまざまなシステムや技術にわたる包括的な試験に適した汎用性の高いツールです。技術の進歩と新しい周波数帯域の導入に伴い、複数の帯域に迅速に適応し、複数の帯域間を切り替えることができる機器のニーズがますます高まっています。

スペクトラム アナライザで高速周波数ホッピング手法を利用すると、掃引時間が短縮され、過渡信号を検出する能力が向上するため、高速かつ正確な測定が可能になります。複数の NCO を搭載、または FRI のような高速再構成方式を採用した先進的な ADC の高速スイッチング機能を使用すると、広い周波数範囲にわたってより効率的な分析が可能となり、研究アプリケーションおよびとフィールド アプリケーションの両方で、スペクトラム アナライザの総合的な性能と有用性が向上します。

ワイヤレス テスタでは、高速周波数ホッピング手法は、通信システムの特性評価とトラブルシューティングにおいて重要な役割を果たします。これらの手法により、周波数間の迅速な遷移が可能になり、信号の忠実度が向上し、テスト サイクルが短縮されます。この機能は、複数の周波数条件下でワイヤレス デバイスの性能を評価する際に特に重要です。

スペクトラム アナライザやワイヤレス テスタ以外にも、高速周波数ホッピング手法は多くの試験 / 測定機器アプリケーションに大きな利点をもたらします。たとえば、汎用信号アナライザや RF 信号ジェネレータは、これらの手法を活用して、複数の周波数帯域で柔軟かつ正確に試験を実施できます。また、マルチバンド レシーバは、帯域をすばやく切り替えることができるため、動的な試験環境で信頼性の高い性能を確保できます。

5 まとめ

高速周波数ホッピング手法は、周波数間を高速かつ高精度に遷移できるようにすることで、柔軟性と精度を向上し、進化する技術ニーズにより良く適応できるようにします。試験 / 測定機器に対する要求が増大し続ける中、最先端の性能を維持し、包括的な試験能力を確保するには、高速周波数ホッピング方式を理解し、実装することが不可欠です。

6 関連ウェブサイト

- Wood, Chase、2024 年、『ADC Decimation: Addressing High Data-Throughput Challenges』、Embedded Computing Design、2024 年 2 月 5 日。

- Wood, Chase、2024 年、『ADC Decimation: Unlocking RF Potential with Downconverters』、Embedded Computing Design、2024 年 2 月 29 日。

- Wood, Chase、2024 年、『ADC Decimation: Analyzing High-Bandwidth Spectrum Clusters』、Embedded Computing Design、2024 年 5 月 9 日。

- テキサス・インスツルメンツ ADC32RF55 データシート

- テキサス・インスツルメンツ DAC39RF12 データシート

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2024, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社