JAJT349 September 2024 TPLD1201 , TPLD1201-Q1 , TPLD1202 , TPLD1202-Q1 , TPLD801 , TPLD801-Q1

ロジック デバイスは、あらゆるエレクトロニクス設計の接着剤であるとよく言われますが、システムの部品を選択するときに考慮すべき最後の部品ということも珍しくありません。十分に試されて信頼できる標準ロジック デバイスは数多く存在し、その中から選ぶことができます。しかし、設計はますます複雑になってきているため、多くの機能を搭載するスペースを確保するために、基板上のロジック要素を統合する必要も強まっています。

エンジニアは、ソリューションのサイズを減らし、設計と製造のコストを削減して、サプライ チェーンを管理し、市場投入までの期間を短縮するため、プログラマブル ロジック デバイス (PLD)、複合 PLD (CPLD)、フィールド プログラマブル ゲート アレイ (FPGA) を選択するようになってきています。CPLD や FPGA は数千ものロジック要素をサポートし、さまざまなパッケージ サイズが存在するため、これらを使用して設計を行うときは、多くのトレードオフを考慮する必要があるほか、高度なソフトウェア プログラミングの専門知識が必要になる場合があります。

TI の PLD ポートフォリオに記載されているような新しい PLD は、数十ものシーケンシャル ロジックとアナログの機能を 1 つのパッケージに統合しているため、ディスクリート ロジックの実装に比べて総合的に基板面積を 90% 以上、部品点数を 80% 以上削減できます。単一の業界標準パッケージに統合されている TI 機能のいくつかを、図 1 に示します。

適切なサイズの構成可能ロジック

TI の PLD 製品ラインアップには、ロジック機能、D タイプのフリップ フロップ、パイプ遅延、パターン ジェネレータ、カウンタ、遅延、コンパレータなどを統合した製品が含まれています。異なる、または新しい機能やパラメータをサポートするためにハードウェアの設計を変更する必要はなくなります。その代わりに、標準および構成可能なロジック要素を使用して、必要なパフォーマンスを提供するソリューションを開発できます。TI の PLD を使用すればソフトウェア開発が不要で、ハードウェア記述言語のコーディング経験も必要ありません。

図 1 に、TPLD1201 の構成可能なロジック要素の概要を示します。

図 1 TPLD1201 のブロック図 - 構成可能ロジック

図 1 TPLD1201 のブロック図 - 構成可能ロジック業界標準パッケージのプログラマブル ロジック

現在市場に出回っている PLD の多くは、コンシューマ エレクトロニクス アプリケーションをサポートするための特定用途向けパッケージで供給されています。TI の PLD は、標準的な JEDEC (Joint Electron Device Engineering Council、半導体技術協会) のリード付きパッケージとリードなしパッケージのオプションを使用しているので、車載用と産業用のアプリケーションでプログラマブル ロジックを容易に実装できます。TI の PLD ポートフォリオには、0.5mm ピッチのリード付きパッケージが含まれており、半田付けと自動光学検査を支援し、システムの安全性と長期的な信頼性を保証確保します。これらのデバイスは、40℃から 125℃までの拡張温度範囲と、AEC (Automotive Electronics Council、車載電子部品評議会) Q-100 認定に対応しています。

わずかな時間で構成可能

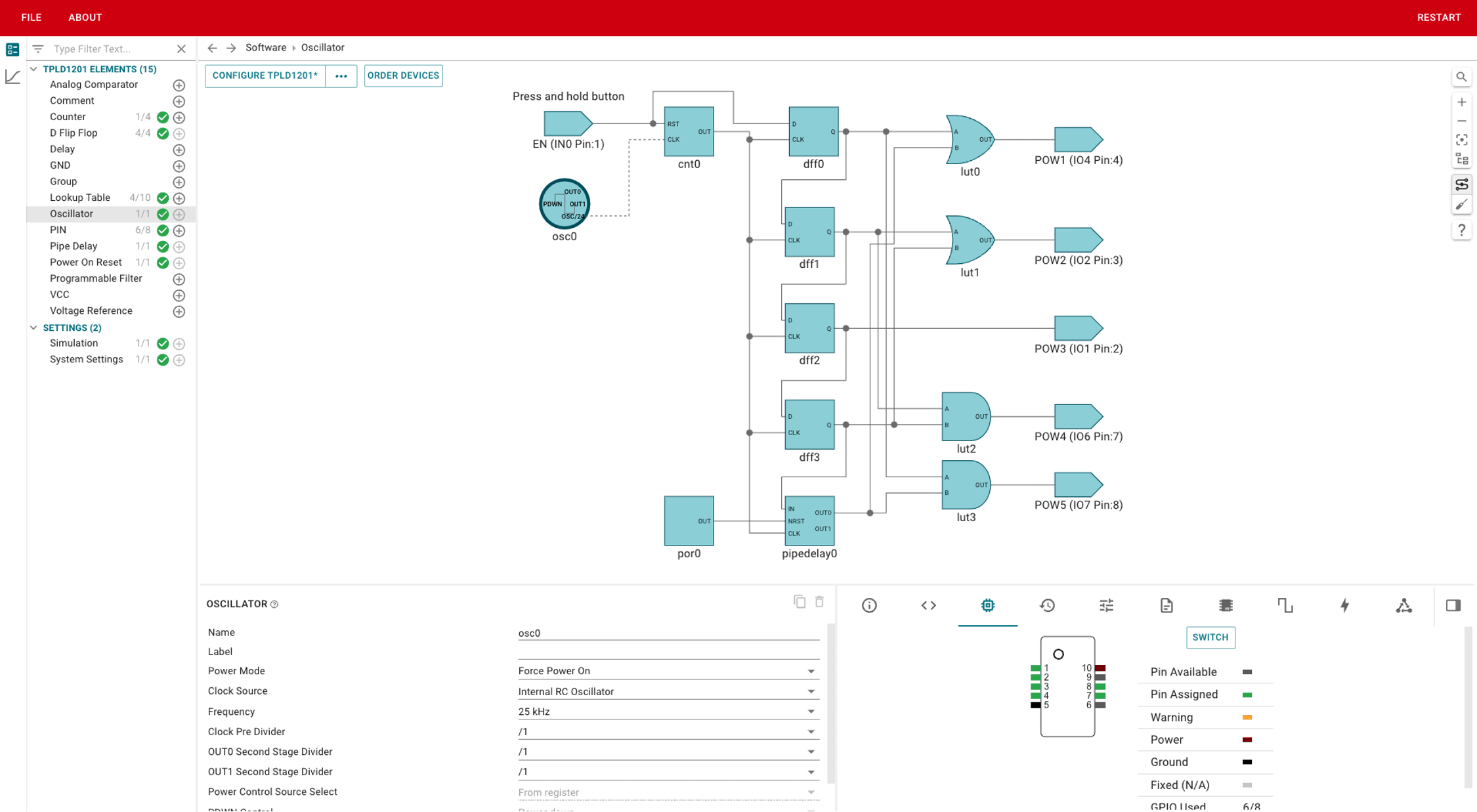

TI の PLD は、使いやすいグラフィカル インターフェイスを使用して目的の回路を構成することで、プログラミング プロセスを簡略化できます。ロジック回路を設計した後で、評価用にデバイスを一時的に構成するか、最終製品で使用できるようデバイスを永続的にプログラムできます。TI は、設計者を念頭に InterConnect Studio を作成しました。これによって、コーディング経験なしでも TI の PLD を構成可能になります。InterConnect Studio を使用すると、開発とシミュレーションをわずか数分で完了し、プロトタイプを数秒で作成できます。

InterConnect Studio による電源シーケンス アプリケーションの回路設計を、図 2 に示します。

図 2 TI の TPLD1201 を使用した電源シーケンス アプリケーションを InterConnect Studio のデスクトップで表示

図 2 TI の TPLD1201 を使用した電源シーケンス アプリケーションを InterConnect Studio のデスクトップで表示GUI の左側にあるメニューから、要素の横にあるプラス記号を選択して、別のコンポーネントを追加できます。コンポーネント間のドラッグ アンド ドロップ接続を簡単に作成し、メイン ウィンドウの下のメニューでさらに微調整できます。

回路を設計してシミュレーションを実行してから [TPLD の構成] ボタンを押すと、TPLD プログラマや評価基板を使用して、デバイスを簡単に一時的に構成できます。デバイスを永続的にプログラムする場合は、メニューでチェック ボックスを選択します。

まとめ

現在は、設計者向けのプログラマブル ロジック ソリューションが多数存在します。TI の PLD はより小型のパッケージ オプションで使用できるため、より高度なプログラマブル製品に比べて、プリント基板の小型化、製造コストの削減、超低消費電力、ロジック要素の削減、アナログ機能、プログラミングの簡素化を実現できます。確実なのは、プログラマブル ロジックでアプリケーションの要件を満たすため、これまでより多くの選択肢から選べるようになるということです。

その他の資料

- TI の PLD ポートフォリオをご覧ください:PLD ポートフォリオ。

- TI の PLD 製品を比較するには、このパラメータ表をご覧ください。

- アプリケーション ノート『TI のプログラマブル ロジック デバイスによる、フィードバック付き電源シーケンス』をご覧ください。

- プログラマブル ロジックでのルックアップ テーブルの使用方法の詳細をご覧ください。

商標

すべての商標はそれぞれの所有者に帰属します。