JAJU751G September 2019 – October 2023

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

-

2システム概要

- 2.1 ブロック図

- 2.2 設計上の考慮事項

- 2.3

主な使用製品

- 2.3.1 LMG3422R050 — ドライバと保護機能を内蔵した 600V GaN

- 2.3.2 TMCS1100 — 高精度絶縁型電流センス・モニタ

- 2.3.3 UCC27524 — デュアル、5A、高速 2 次側パワー MOSFET ドライバ

- 2.3.4 UCC27714 — 620V、1.8A、2.8A 1 次側 / 2 次側ゲート・ドライバ

- 2.3.5 ISO7721 — 高速、堅牢な EMC 特性、強化絶縁型、基本デュアル・チャネル・デジタル・アイソレータ

- 2.3.6 ISO7740 および ISO7720 — 高速、低消費電力、堅牢な EMC デジタル・アイソレータ

- 2.3.7 OPA237 — 単一電源オペアンプ

- 2.3.8 INAx180 — 2 次側および 1 次側電圧出力、電流センス・アンプ

- 2.3.9 TPS560430 — SIMPLE SWITCHER 4V~36V、600mA、同期整流降圧コンバータ

- 2.3.10 TLV713 — ポータブル機器向けフォールドバック電流制限付き 150mA 低ドロップアウト (LDO) レギュレータ

- 2.3.11 TMP61 — 温度検出向けシリコン・ベース小型リニア・サーミスタ

- 2.3.12 CSD18510Q5B — 40V、N チャネル NexFET MOSFET、シングル SON5x6、0.96mΩ

- 2.3.13 UCC28911 — 定電圧、定電流、1 次側レギュレーション付き 700V フライバック・スイッチャ

- 2.3.14 SN74LVC1G3157DRYR — 単極双投アナログ・スイッチ

- 2.4 システム設計理論

-

3ハードウェア、ソフトウェア、テスト要件、テスト結果

- 3.1

必要なハードウェアとソフトウェア

- 3.1.1 ハードウェア

- 3.1.2 PFC 段ソフトウェア

- 3.1.3 LLC 段ソフトウェア

- 3.1.4 PFC + LLC 段のデュアル・テスト

- 3.1.5 ライブ・ファームウェア・アップデートの概要

- 3.2 テストと結果

- 3.1

必要なハードウェアとソフトウェア

- 4設計ファイル

- 5ソフトウェア・ファイル

- 6関連資料

- 7著者について

- 8改訂履歴

- 132

3.1.2.2 プロジェクト構造

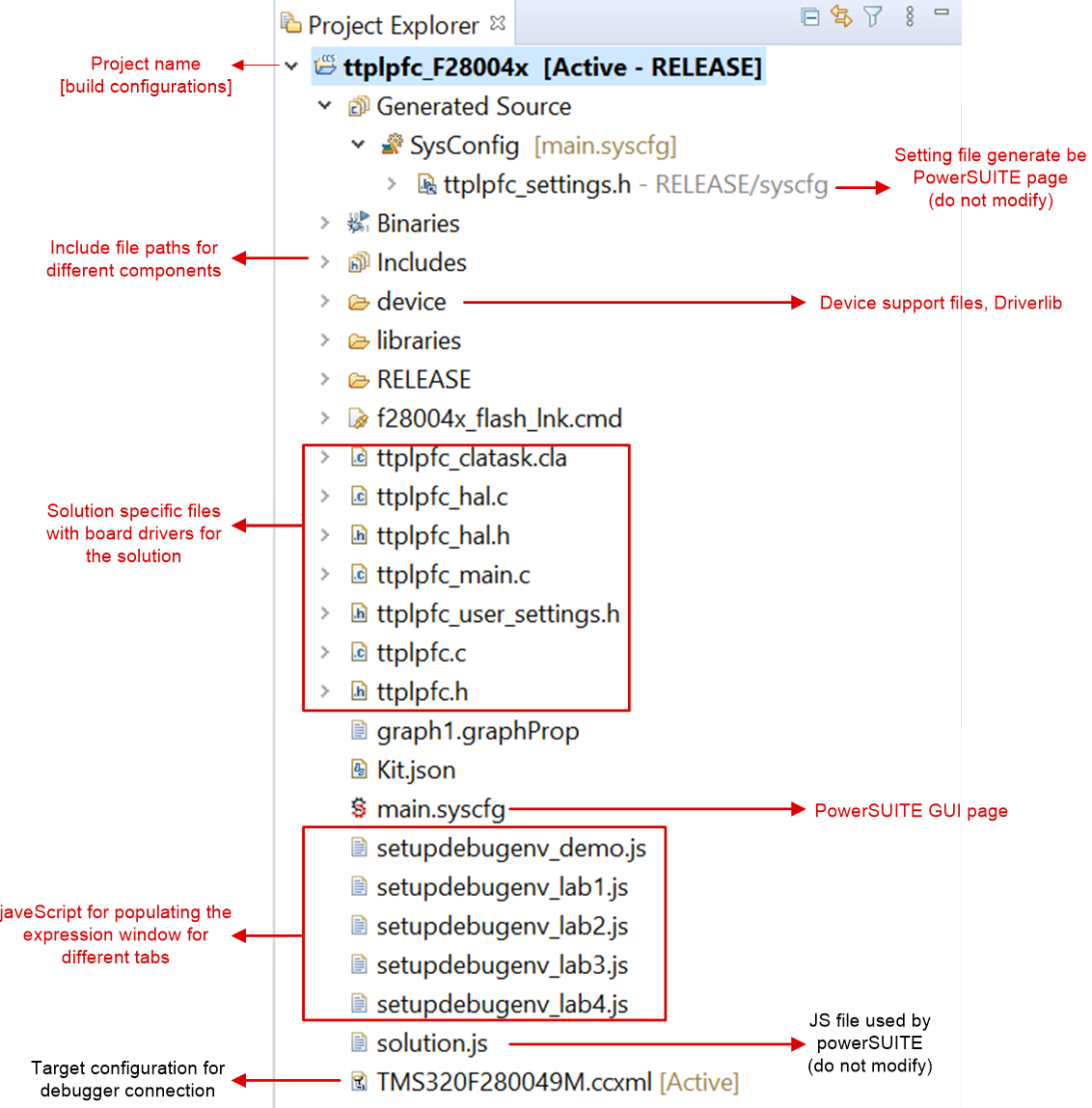

プロジェクトがインポートされると、図 3-2 に示すように CCS 内に Project Explorer が表示されます。

図 3-2 PFC ソリューション・プロジェクトの Project Explorer ビュー

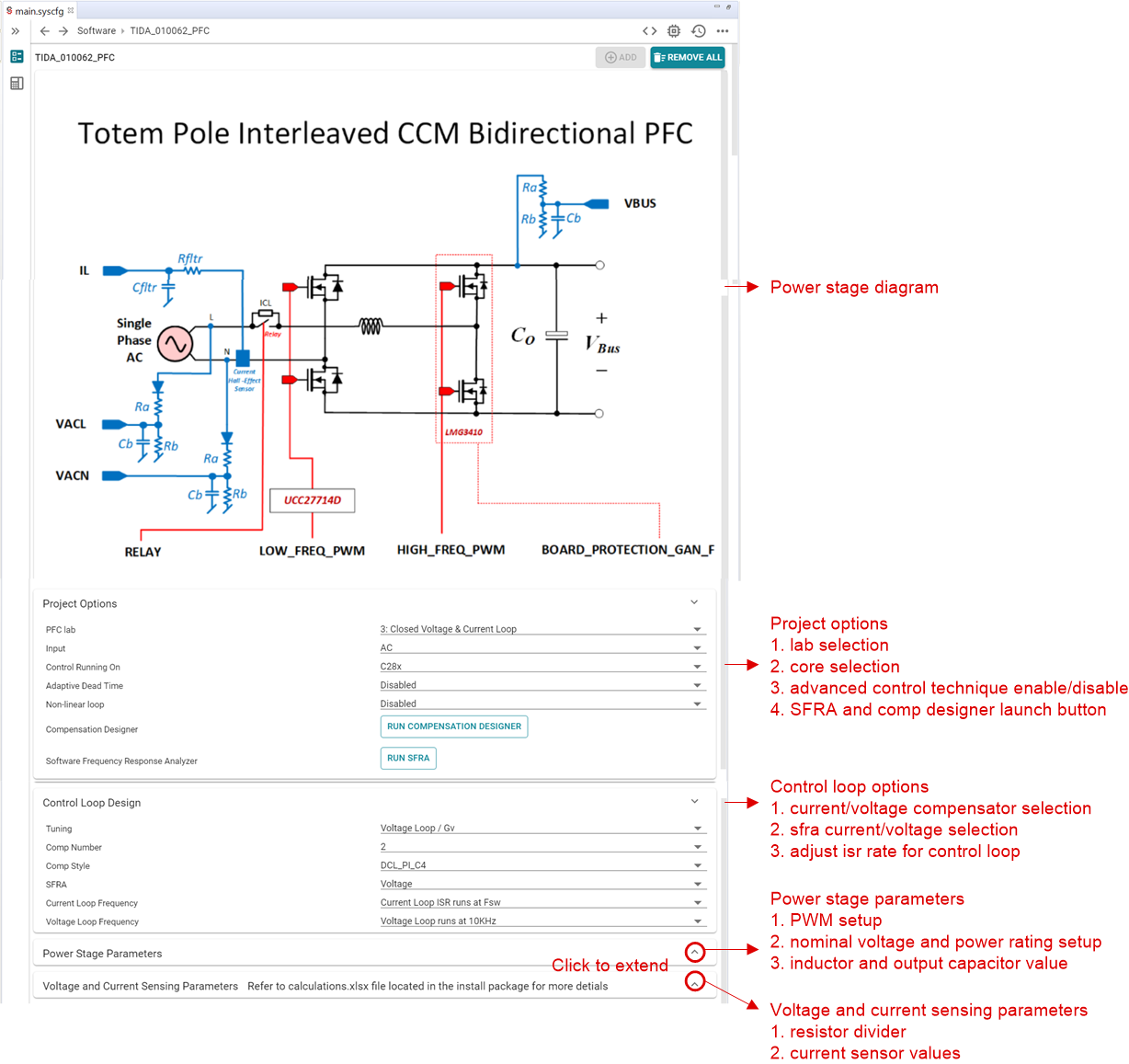

main.syscfg ファイルをクリックすると、GUI ページが表示され、PFC ソリューションの変更可能なオプションが表示されます (図 3-3)。この GUI を使用して定格電力、インダクタンス、容量、検出回路パラメータなど、適合ソリューションのパラメータを変更できます。

図 3-3 CCM TTPL PFC 段の powerSUITE ページ

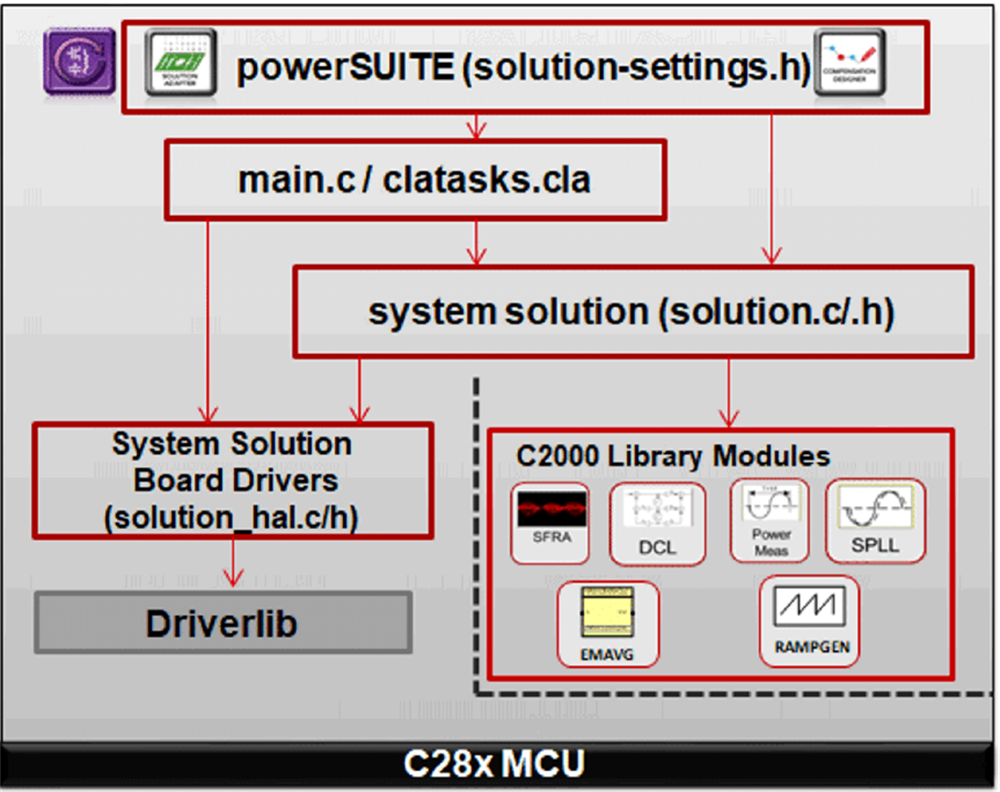

プロジェクトの一般構造を図 3-4 に示します。

図 3-4 プロジェクト構造の概要

図 3-4 は F28004x/F28002x/F28003x のプロジェクトを示していますが、powerSUITE ページから別のデバイスを選択しても、その構造は同様です。

ソリューション別でデバイスに依存しないファイルは <solution>.c/h です。 このファイルはプロジェクトの main.c ファイルで構成されており、各ソリューションの制御構造に関与します。

この設計のこの段階では、<solution> は ttplpfc です。

基板別でデバイス別のファイルは <solution>_hal.c/h です。 このファイルは、各ソリューションを実行するデバイス別ドライバで構成されています。

powerSUITE ページは、Project Explorer に表示される main.syscfg ファイルをクリックして開くことができます。 powerSUITE ページでは <solution>_settings.h ファイルが生成されます。 このファイルは、powerSUITE ページで生成されたプロジェクトのコンパイル時に使用する唯一のファイルです。プロジェクトが保存されるたびに powerSUITE によって変更内容が上書きされるため、このファイルを手動で変更しないでください。<solution>_user_settings.h ファイルで、いくつかの設定を変更できます。

Kit.json ファイルと solution.js ファイルも、powerSUITE により内部で使用されるため、ユーザーが変更することはできません。 これらのファイルを変更すると、プロジェクトが正常に機能しなくなります。

setupdebugenv_build.js は、さまざまなラボで [Watch] ウィンドウの変数を自動入力するために提供されています。

*.graphProp ファイルは、データ・ロガー・グラフの設定を自動入力するために提供されています。

プロジェクトは、PWM サイクルごとに呼び出される割り込みサービス・ルーチン (ISR) で構成されており、この ISR の中で電流コントローラが実行されます。ほかにも電圧ループおよび計測 ISR を実行するために呼び出される、約 10kHz の低速 ISR があります。少数のバックグラウンド・タスク (A0-A4 および B0-B4) はポーリング方式で呼び出され、これを使用して SFRA バックグラウンドなど、絶対的なタイミング精度が要求されない低速タスクを実行できます。

図 3-5 にファームウェアのソフトウェア・フローチャートを示します。

図 3-5 PFC 段のソフトウェア構造

図 3-5 PFC 段のソフトウェア構造システムの開発および設計を簡素化するために、このリファレンス・デザインのソフトウェアは、次の 4 つのラボで構成されています。lab1 と lab2 は、昇圧 DC/DC 動作を検証するように設計されています。lab3 および lab4 は、PFC AC/DC 動作を検証するように設計されています。

これらのラボについてはセクション 3.1.2.5 に詳述します。リファレンス・デザイン・ハードウェアを使用する場合は、セクション 3.1.1 で述べたようにハードウェア設定が完了していることを確認します。