NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

1 MSPM0L 硬體設計檢查清單

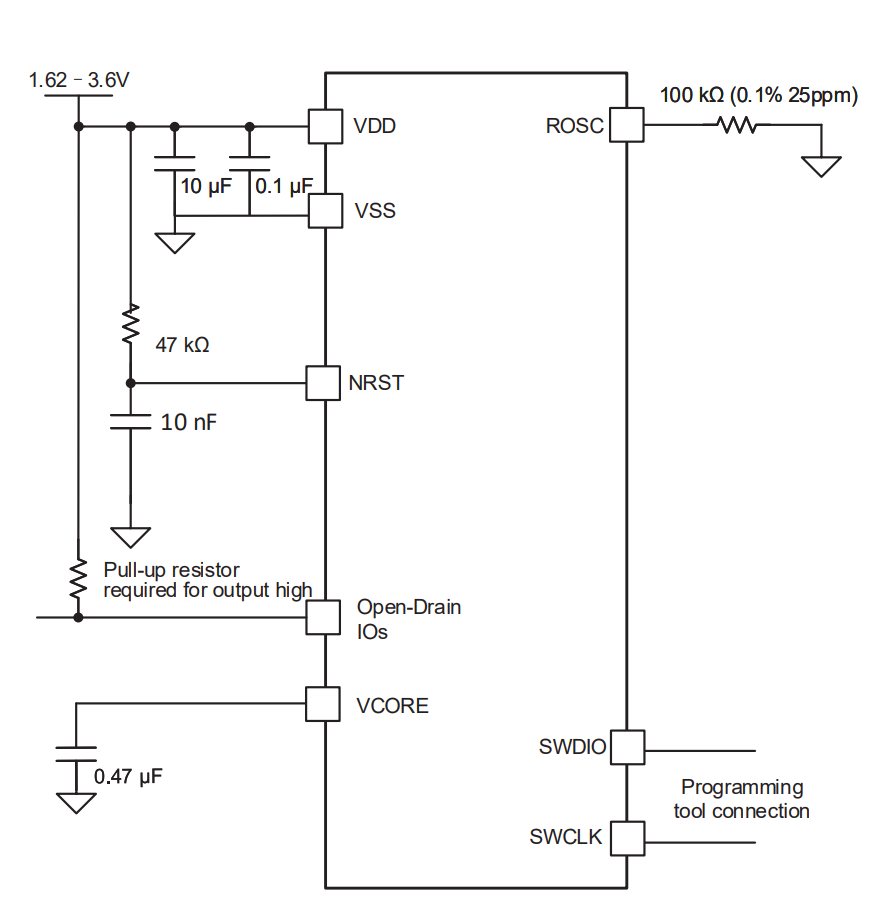

表 1-1 說明在 MSPM0L 硬體設計過程需要檢查的主要訊號。以下各節將提供更多詳細資訊。

表 1-1 MSPM0L 硬體設計檢查清單

| 接腳 (1) | 說明 | 需求 |

|---|---|---|

| VDD | 電源供應器正極接腳 | 在 VDD 和 VSS 間放置 10-µF 和 100-nF 電容器,並使其靠近 VDD 和 VSS。 |

| VSS | 電源供應器負極針腳 | |

| VCORE | 核心電壓 (典型:1.35 V) | 將 470-nF 電容器連接到 VSS,不要提供任何電壓或對 VCORE 接腳施加任何外部負載。 |

| NRST | 重設針腳 | 使用 10-nF 下拉電容器連接外部 47-kΩ 上拉電阻器。 |

| ROSC | 外部參考電阻器接腳 |

|

| VREF+ | 外部參考輸入的電壓參考電源 |

|

| VREF- | 外部參考輸入的電壓參考接地電源 | |

| SWCLK | 偵錯探測器的序列線時鐘 | 內部上拉至 VDD,不需任何外部零件。 |

| SWDIO | 雙向 (共用) 序列線路數據 | 內部下拉至 VSS,不需任何外部零件。 |

| PA0、PA1 | 開汲極 I/O | 高輸出所需的上拉電阻器 |

| PA18 | 預設 BSL 叫用接腳 | 保持下拉以避免在重設後進入 BSL 模式。BSL 叫用接腳可重新對應。 |

| PAx (PA0、PA1 除外) | 通用 I/O | 將對應針腳功能設爲 GPIO (PINCMx.PF = 0x1),並將未使用的針腳配置爲低輸出,或使用內部上拉電阻或下拉電阻輸入。 |

| OPAx_IN0-(2) | OPAx 反相終端輸入 0 | 此接腳爲高阻抗,不需要任何外部零件 (若未使用)。 |

(1) 針對任何與通用 I/O 共用函數的未使用接腳,請遵循「PAx」未使用接腳連接準則。

(2) 僅限 MSPM0L134x

TI 建議將 10-μF 和 0.1-nF 低 ESR 陶瓷去耦電容器組合連接到 VDD 和 VSS 接腳。可使用數值較高的電容器,但會影響電源供應軌上升時間。去耦電容器的位置必須儘可能靠近去耦的接腳 (應在數毫米內)。

將外部 47-kΩ 上拉電阻器與 10-nF 下拉電容器連接時需要 NRST 重設針腳。

SYSOSC 頻率修正迴路 (FCL) 電路利用位於 ROSC 針腳和 VSS 間的外部 100-kΩ 電阻器,為 SYSOSC 提供精確的參考電流,以穩定 SYSOSC 頻率。如果未啓用 SYSOSC FCL,則不需要此電阻器。

VCORE 接腳需要 0.47-µF 槽型電容器,且必須置於距離裝置接地最小距離的裝置附近。

若為 5-V 容錯開汲極 (ODIO),需要上拉電阻器才能有高輸出,如果使用 ODIO 則需此電阻器以提供 I2C 和 UART 功能。

圖 1-1 MSPM0L 典型應用程序電路圖

圖 1-1 MSPM0L 典型應用程序電路圖