NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

2.1 數位電源供應

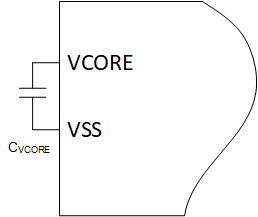

VCORE 穩壓器

內部低壓降線性穩壓器會產生 1.35-V 電源軌為裝置核心供電。一般而言,核心穩壓器輸出 (VCORE) 會為核心邏輯供電,其中包括 CPU、數位周邊設備和裝置記憶體。核心穩壓器需要連接裝置 VCORE 接腳與 VSS (接地) 的外部電容器 (CVCORE) (請參閱 圖 2-1)。有關 CVCORE 的正確值和容差,請參閱裝置特定產品規格表。CVCORE 應置於 VCORE 接腳附近。

核心穩壓器在所有電源模式下都處於啟用狀態,但關機模式除外。在其它所有電源模式 (執行、睡眠、停止和待機) 下,穩壓器的驅動強度將自動配置爲支援每種模式的最大負載電流。使用低功耗模式時會降低穩壓器的靜態電流,進而提升低功耗效能。

圖 2-1 VCORE 穩壓器電路

圖 2-1 VCORE 穩壓器電路