NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

9.4 如何選擇電路板層及建議的堆疊

為減少高速訊號的反射,必須符合源極、汲極與傳輸線路間的阻抗。訊號軌跡的阻抗取決於其幾何及其與於任何參考平面的相對位置。

特定阻抗需求的差動對間軌跡寬度與間距,將視所選 PCB 堆疊而定。由於最小軌跡寬度和間距有所限制,且需視 PCB 技術類型和成本需求而定,因此需選擇 PCB 堆疊以實現所有必要的阻抗。

可使用的最低配置爲 2 個堆疊。高密度 PCB 需要 4 或 6 層電路板,才能產生多個高速訊號。

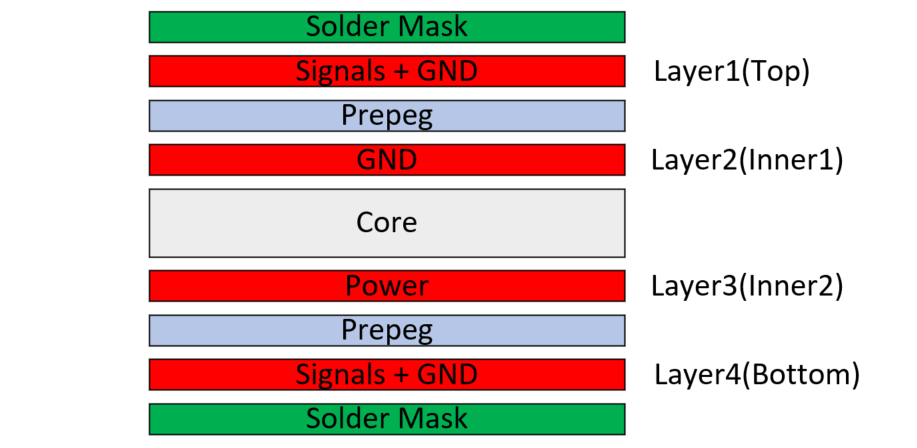

以下堆疊 (請參閱 圖 9-5) 為 4 層範例,可作爲幫助堆疊評估和選擇的起點。這些堆疊配置使用鄰近電源平面的 GND 平面,以增加電容並縮小 GND 與電源平面間的差距。因此上層的高速訊號會有穩固的 GND 參考平面,有助於減少 EMC 排放,因為增加層數和讓每個 PCB 訊號層有 GND 參考,將可進一步提升輻射 EMC 效能。

圖 9-5 四層 PCB 堆疊範例

圖 9-5 四層 PCB 堆疊範例如果系統不是很複雜、沒有高速訊號或一些敏感類比訊號,2 個堆疊架構便已足夠。