SBAA525A september 2021 – may 2023 AFE7900 , AFE7920 , AFE7950

2.1.1.2 ADC to DAC Low Latency Loopback

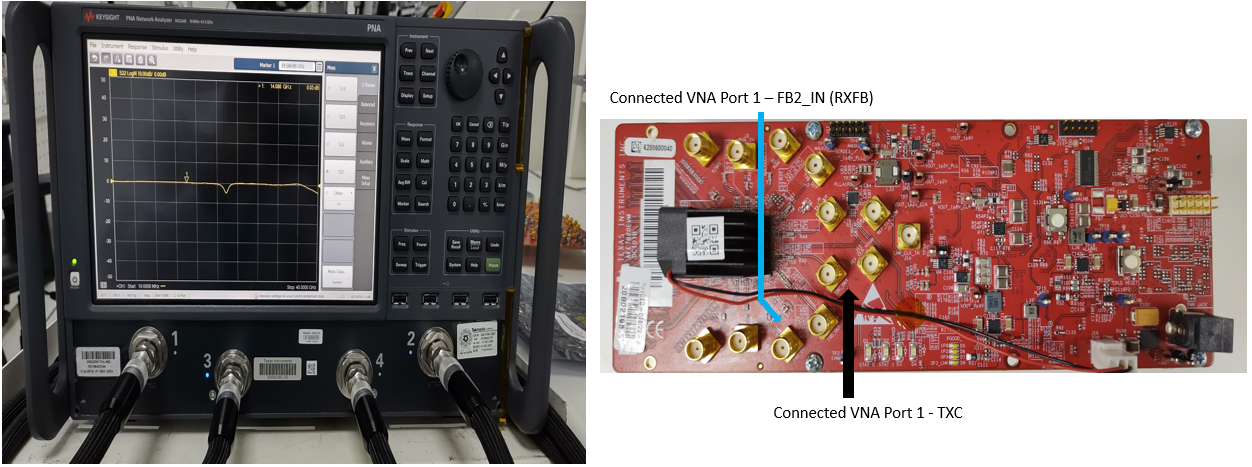

Vector Network Analyzer port 2 is connected to FBCD channel of device, TXC channel is reconnected to port 1 of Vector Network Analyzer to capture group delay and loop gain. Vector Network Analyzer internally sweeps across bandwidth relative to Impedance matching bandwidth.

Figure 2-2 HW Block Diagram – Low Latency Loopback

Figure 2-2 HW Block Diagram – Low Latency Loopback