SLAAEH2A December 2023 – June 2024 TAA5212 , TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAD5112 , TAD5212

3.3.4 Custom Mode (Main Fs - Lower rate) with Recording

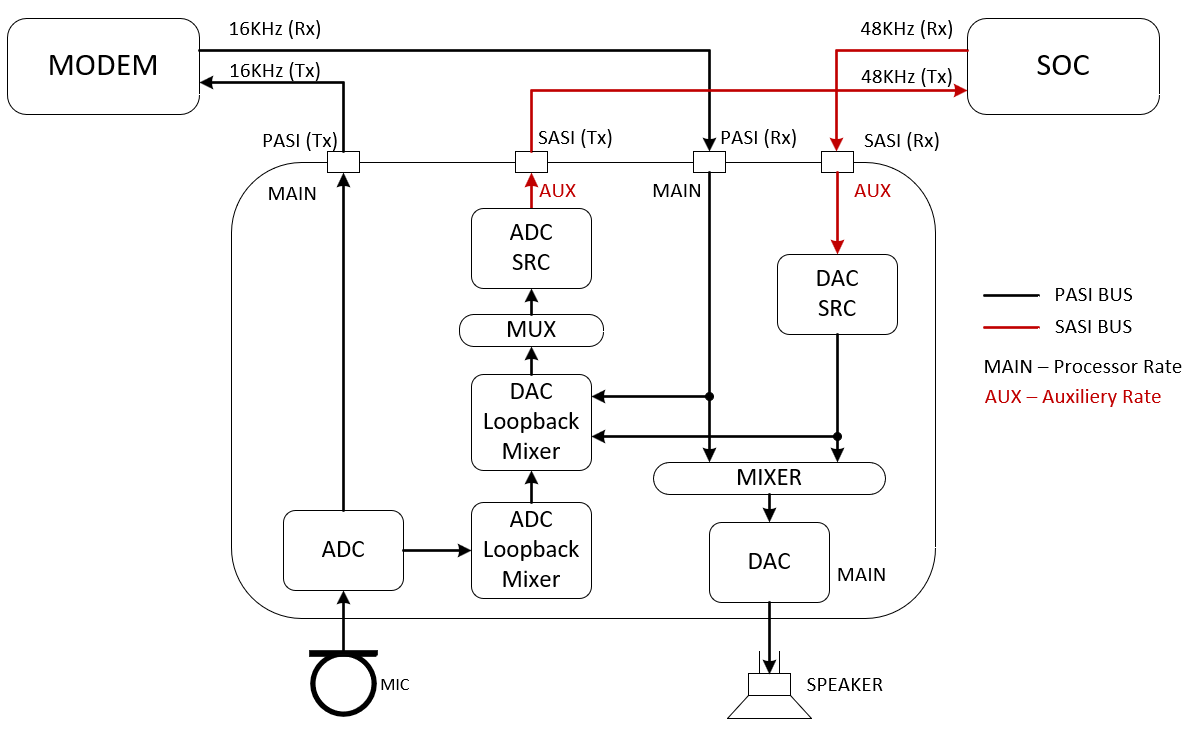

Figure 3-13 shows a block diagram for this use case. PASI is running at 16KHz and SASI is at 48KHz. In this use case analog input (MIC) is sampled at main Fs (lower rate) and send out to PASI TX. The same MIC input can mix with DAC inputs from PASI RX, SASI RX or both and up-sampled with SRC for SASI TX. On the DAC side, SASI RX data can mix with PASI RX data prior to DAC output (Speaker).

Figure 3-13 Custom Mode Diagram with Recording

Figure 3-13 Custom Mode Diagram with RecordingThe Audio Precision APx555 configurations for PASI and SASI is shown below. In this test case mixer coefficients are kept to its default (full-sacle) and the input levels are adjusted as not to exceed the maximum allowed level for example -9dBrG instead of 0dBrG.

|

PASI APx555: Generator: Analog Output (MIC)∶ 1KHz Sine, -9 dBrG (0dBrG = 2Vrms) Analyzer: Input 1∶ Digital audio for PASI Tx with Fs = 16 KHz, TDM, 32 bit depth Input 2∶ Analog input from DAC output (Speaker) SASI APx555: Generator: Digital Output∶ 750Hz Sine, -9 dBFS Analyzer: Input 1∶ Digital audio for SASI Tx with Fs = 48 KHz, TDM, 32 bit depth |

##### PASI lower rate than SASI ADC and DAC SRC Testing with Recording ######

# Target Mode, TDM, 32-bit

# Primary and Secondary ASI, multiple of 48KHz Sampling

# GPIO2=Secondary FSYNC, GPIO1=Secondary BCLK, GPI1=Secondary DIN, GPO1=Secondary DOUT for 4x4

#

w a0 00 00 # Set page 0

w a0 01 01 # Software Reset

w a0 02 09 # Wake up with AVDD > 2v and all VDDIO level

w a0 0a 10 # GPIO1 as input

w a0 0b 10 # GPIO2 as input

w a0 0d 02 # GPI1 as input

w a0 0c 71 # GPO1 as Secondary DOUT

w a0 11 a2 # Enable PASI DIN and Set GPI2A as Secondary FSYNC and GPIO1 as Secondary BCLK

w a0 12 60 # Set GPI1A as Secondary DIN

w a0 18 00 # Enable both Primary and Secondary ASI as independent

w a0 34 40 # PASI BCLK is the input clock source

w a0 19 00 # 1 data input and 1 data output for PASI and SASI

w a0 1a 30 # PASI TDM, 32 bit format

w a0 1e 20 # PASI DOUT Ch1 on TDM slot 0

w a0 1f 21 # PASI DOUT Ch2 on TDM slot 1

w a0 28 20 # PASI DIN Ch1 on TDM slot 0

w a0 29 21 # PASI DIN Ch2 on TDM slot 1

w a0 00 03 # Set page 3

w a0 1a 30 # SASI TDM, 32 bit format

w a0 1e 00 # Tri-state SASI DOUT Ch1 on TDM slot 0

w a0 1f 01 # Tri-state SASI DOUT Ch2 on TDM slot 1

w a0 22 20 # SASI DOUT Ch5 on TDM slot 0

w a0 23 21 # SASI DOUT Ch5 on TDM slot 1

w a0 28 20 # SASI DIN Ch1 on TDM slot 0

w a0 29 21 # SASI DIN Ch2 on TDM slot 1

w a0 00 01 # Set page 1

w a0 17 40 # SR-Converter without auto detect

w a0 18 40 # Use PASI Fs as Main Fs

w a0 2c d0 # Enable DAC, Side Chain and Loopback Mixer

w a0 00 11 # Set page 0x11

w a0 0c 00 00 40 00 # Route Main Ch1 to LDAC2 Mixer, full scale

w a0 14 40 00 00 00 # Route Main Ch2 to RDAC2 Mixer, full scale

w a0 4c 00 00 40 00 # Route AUX Ch1 to LDAC2 Mixer, full scale

w a0 54 40 00 00 00 # Route AUX Ch2 to RDAC2 Mixer, full scale

w a0 5e 40 00 # ADC Loopback Ch1 to SC_LDAC2 Mixer to mix with LDAC2, full scale

w a0 64 40 00 # ADC Loopback Ch2 to SC_RDAC2 Mixer to mix with RDAC2, full scale

w a0 00 00 # Set page 0

w a0 50 00 # ADC Ch1 diff input, 5KOhm, 2Vrms ac-coupled, audio band

w a0 55 00 # ADC Ch2 diff input, 5KOhm, 2Vrms ac-coupled, audio band

w a0 64 20 # Configure OUT1P/M as differential from DAC1

w a0 65 20 # Configure OUT1P LINEOUT 0dB audio band

w a0 66 20 # Configure OUT1M LINEOUT 0dB 2Vrms Differential

w a0 6b 20 # Configure OUT2P/M as differential from DAC2

w a0 6c 20 # Configure OUT2P LINEOUT 0dB audio band

w a0 6d 20 # Configure OUT2M LINEOUT 0dB 2Vrms Differential

w a0 76 cc # Enable Input and Output Ch1 and Ch2

w a0 78 e0 # Power up ADC, DAC and MICBIAS

Test Results

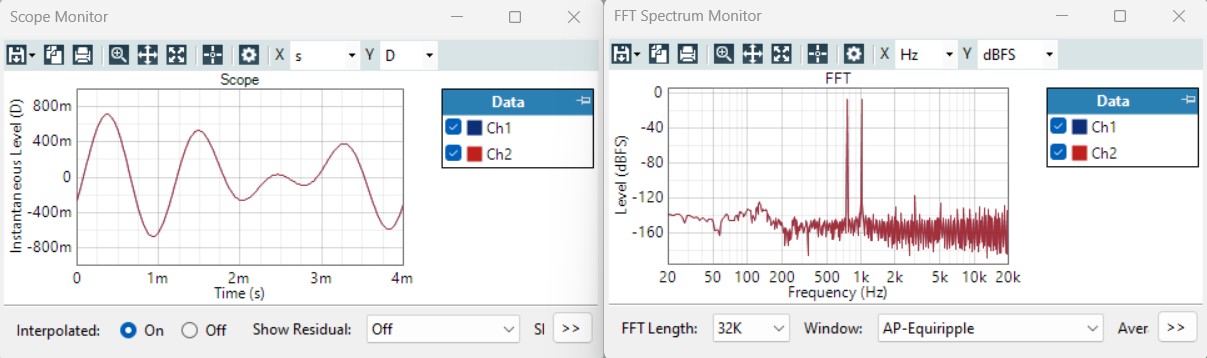

The following plots show the results of the ADC output at SASI after SRC. As seen here the frequency response (FFT) sweeps through 20 KHz (up-sampled to 48 KHz).

Figure 3-14 shows SASI TX output a mixed of MIC input and SASI RX after SRC.

Figure 3-14 SASI ADC output

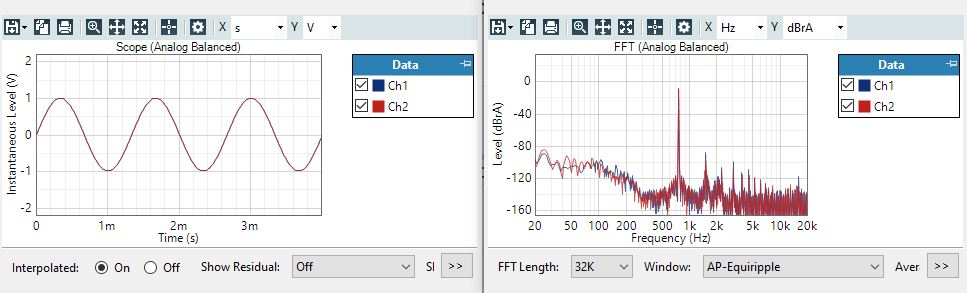

Figure 3-14 SASI ADC outputOn Speaker output, the tone captured is the SASI RX tone of 750 Hz after SRC. PASI RX tone is muted and PASI TX is MIC input of 1 KHz.

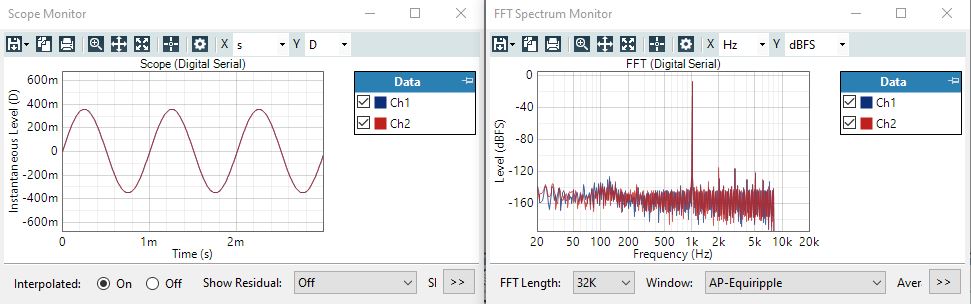

Figure 3-15 shows PASI TX 1KHz tone from MIC input sampled at 16 KHz.

Figure 3-16 shows that this 750 Hz tone is of SASI RX after SRC, PASI tone is off or muted.

Figure 3-15 PASI ADC Output

Figure 3-15 PASI ADC Output Figure 3-16 Speaker Output

Figure 3-16 Speaker Output