SLAU934 September 2024 DAC121S101-SEP

4.2 PCB Layout

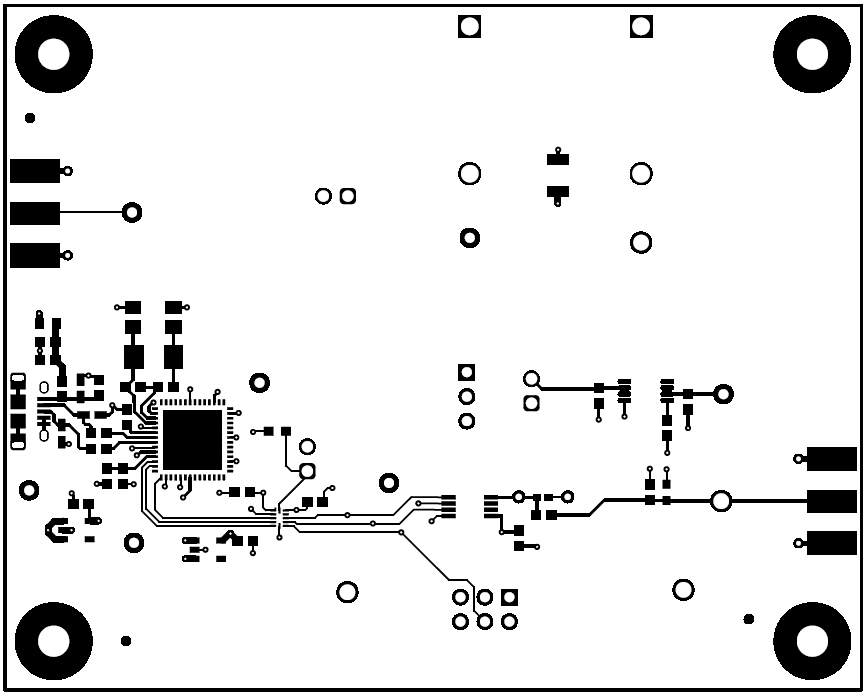

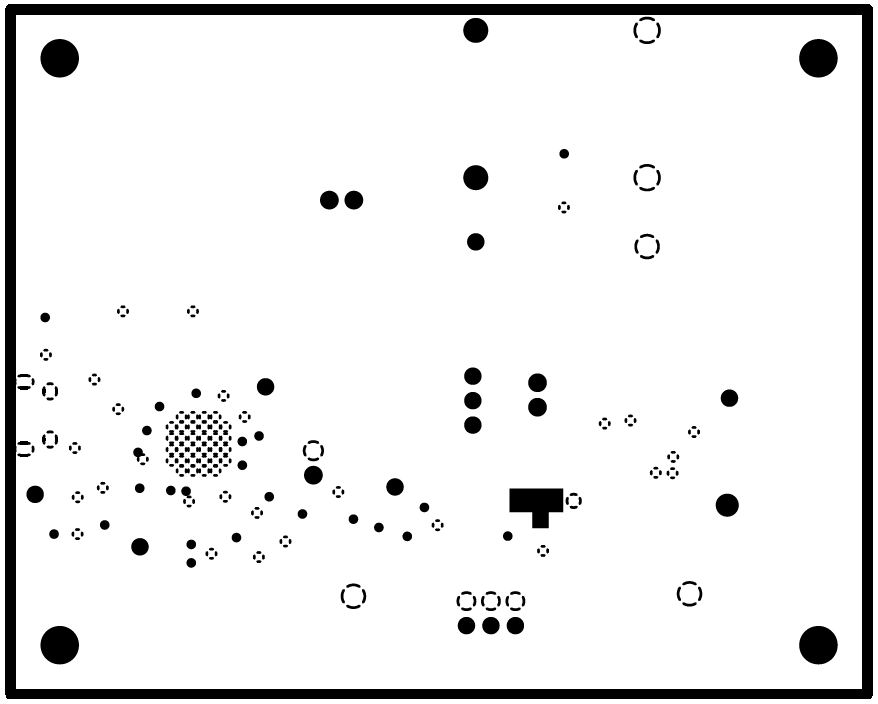

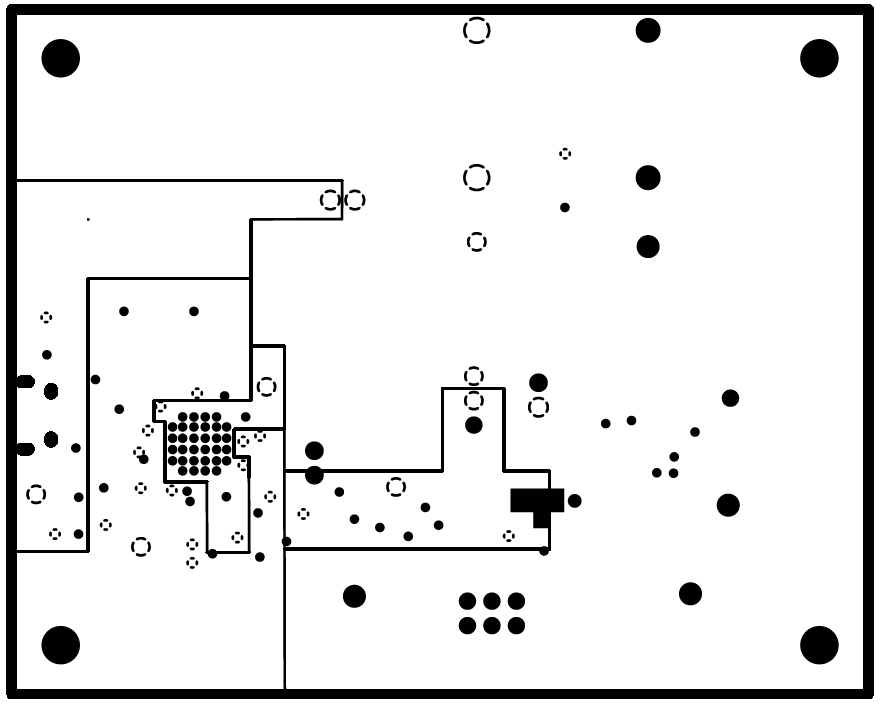

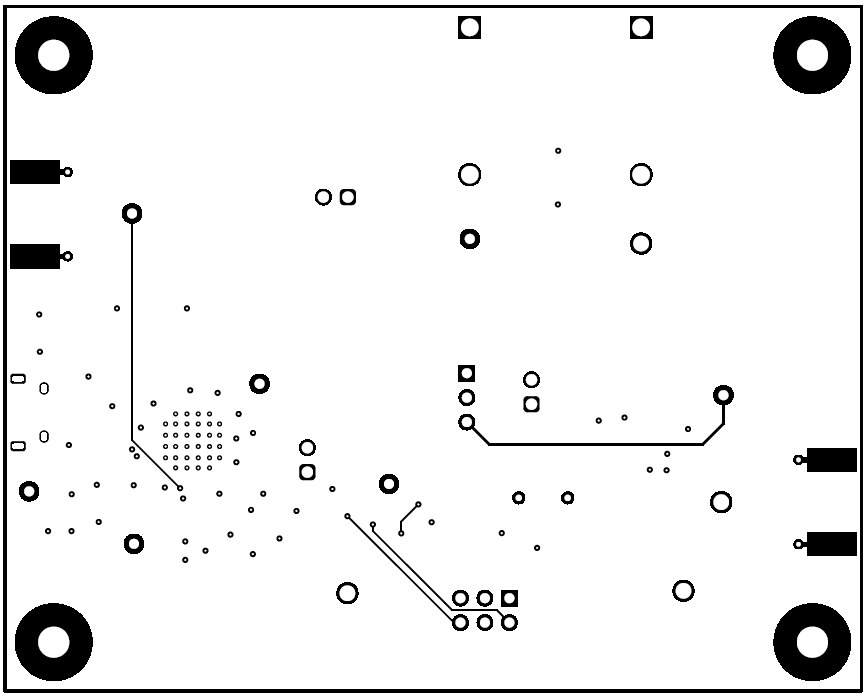

The board layout for the DAC121S101SEPEVM is shown in Figure 4-3 through Figure 4-6.

Figure 4-3 DAC121S101SEPEVM PCB Top Layer Layout

Figure 4-3 DAC121S101SEPEVM PCB Top Layer Layout Figure 4-4 DAC121S101SEPEVM PCB Mid Layer 1 Layout (Ground Plane)

Figure 4-4 DAC121S101SEPEVM PCB Mid Layer 1 Layout (Ground Plane) Figure 4-5 DAC121S101SEPEVM PCB Mid Layer 2 Layout (Power Plane)

Figure 4-5 DAC121S101SEPEVM PCB Mid Layer 2 Layout (Power Plane) Figure 4-6 DAC121S101SEPEVM PCB Bottom Layer Layout

Figure 4-6 DAC121S101SEPEVM PCB Bottom Layer Layout