SLLA641 July 2024 TAA5212 , TAC5112 , TAC5212

3.2.3 Test Case 3: Microphone Maximum Input Level with Gain

In this test case, we add gain from the audio device to -1dBr of the device input full-scale. In the TAX5XXX device, the gain is set through Digital Volume (DVOL) and for ADC6120 device, the gain is set through the PGA register.

From the maximum input level of the microphone measured previously, we apply +19dB gain to bring the record audio path level to -1dBr of full-scale.

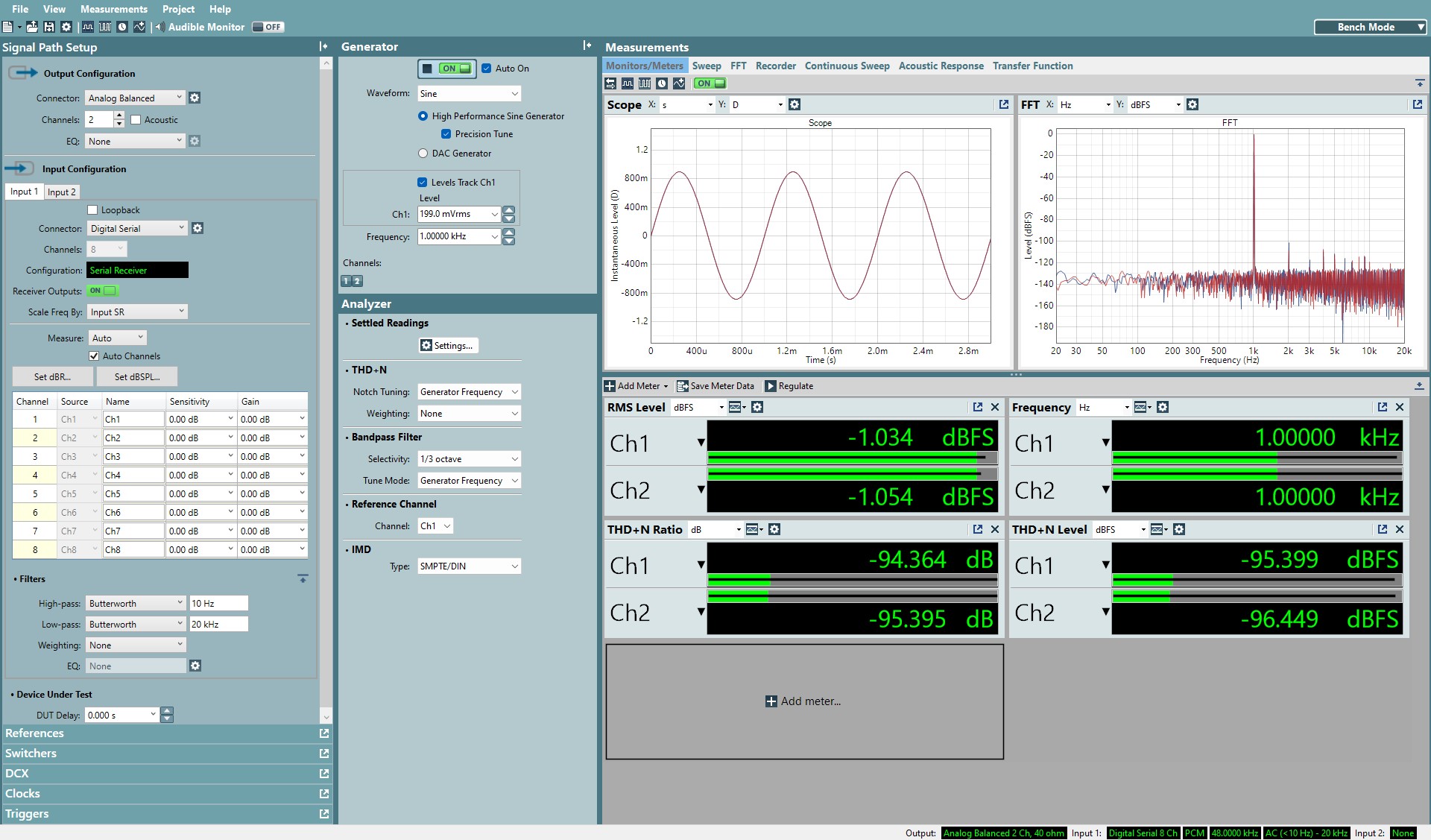

Figure 3-18 TAA5212 Captured of Maximum Mic Input With +19dB Gain

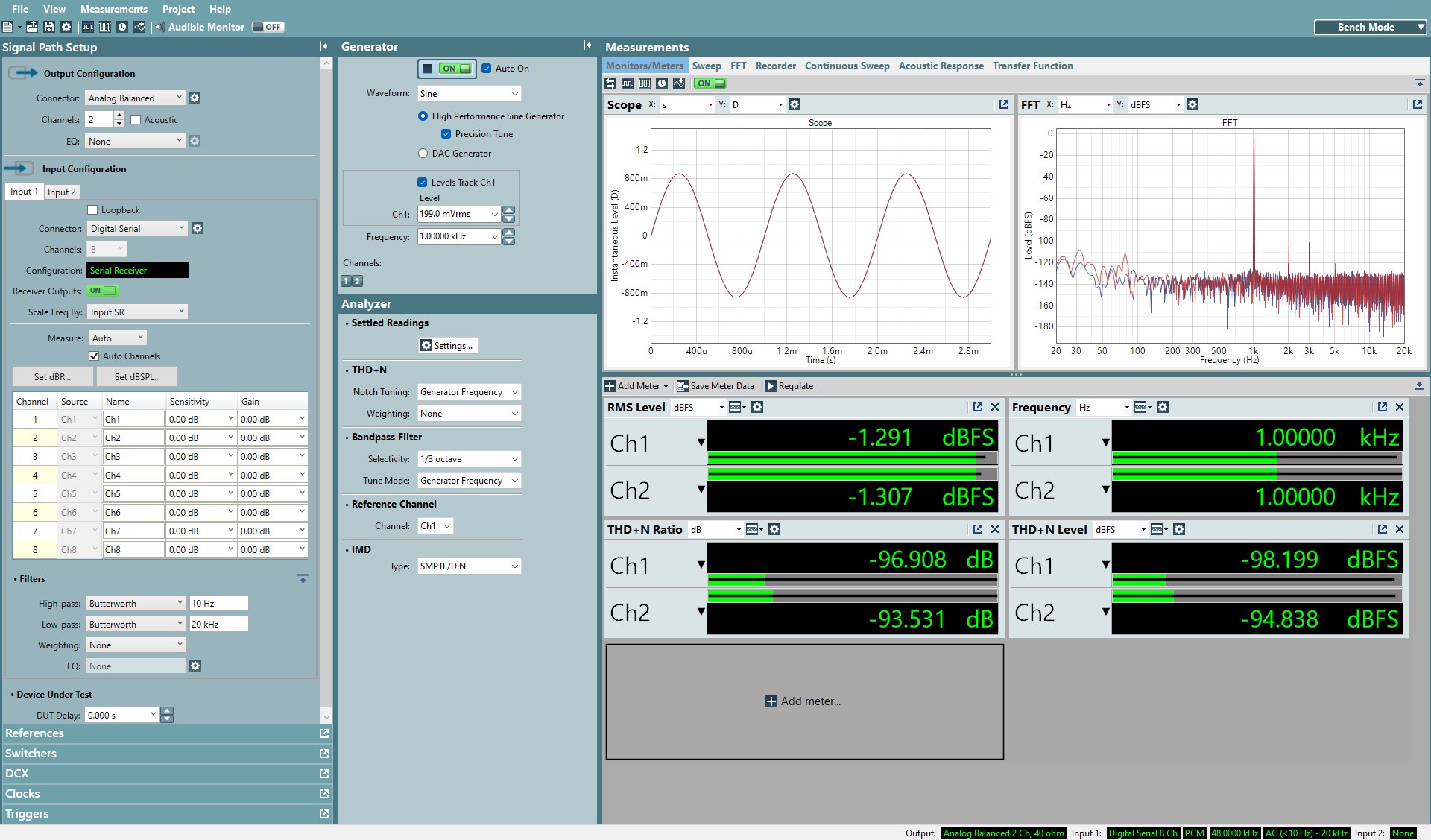

Figure 3-18 TAA5212 Captured of Maximum Mic Input With +19dB Gain Figure 3-19 ADC6120 Captured of Maximum Mic Input With +19dB Gain

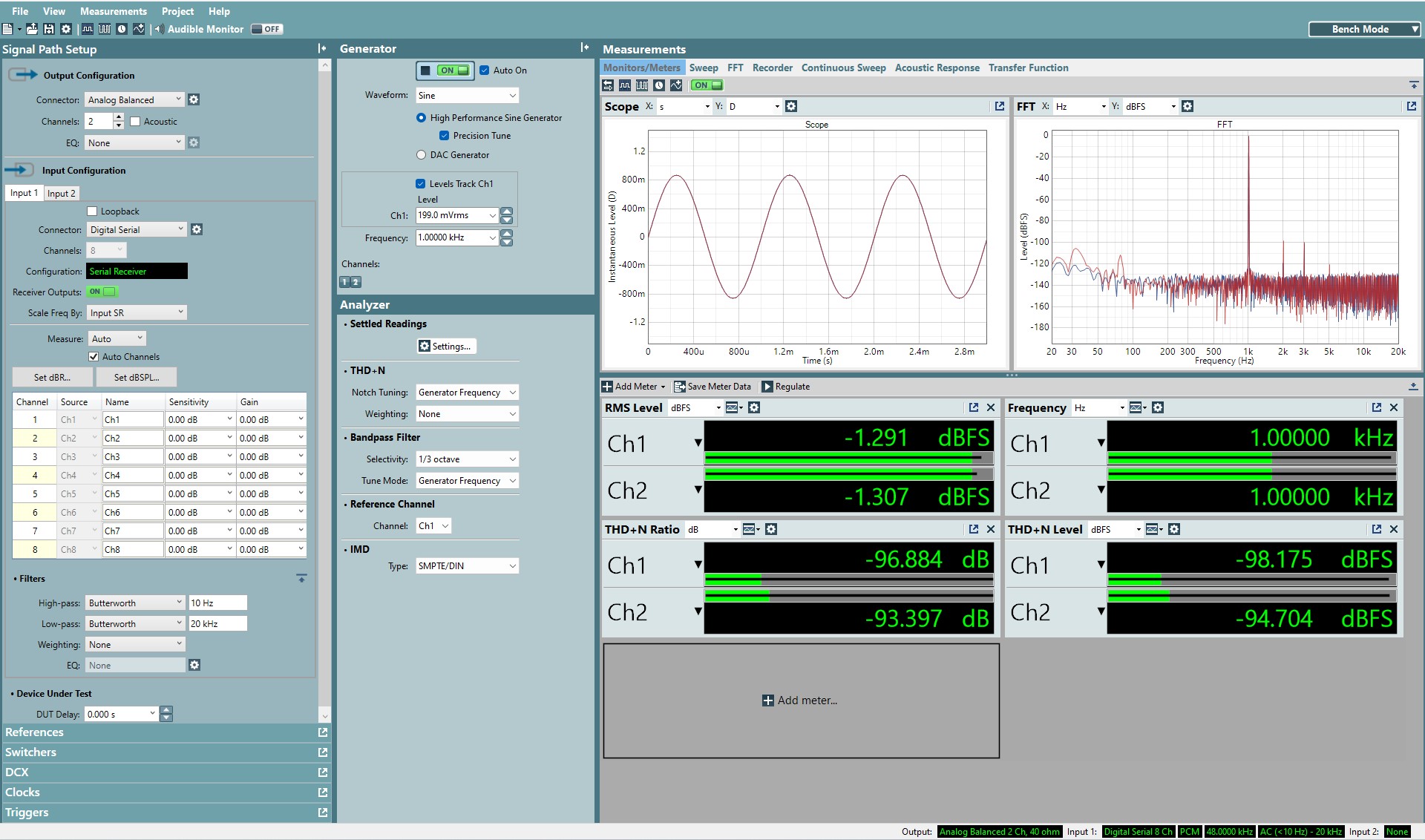

Figure 3-19 ADC6120 Captured of Maximum Mic Input With +19dB Gain Figure 3-20 ADC6120 Captured of Maximum Mic Input With +19dB Gain and DRE Enable

Figure 3-20 ADC6120 Captured of Maximum Mic Input With +19dB Gain and DRE EnableIn TAX5XXX, adding the DVOL gain to the input level does not change the THDN level, but in the ADC6120 device with PGA gain it improves THDN. This increase is due to ADC noise is less dominant than the PGA thus THDN is better.

Table 3-6 MIC 2 Maximum Input Level With +19dB Gain

| Analog Input Vrms [dBr(2Vrms)] | Calculated THDN (dB) | Measured THDN Ratio without Gain (dB) | Measured THDN Ratio with Gain (dB) | |

|---|---|---|---|---|

| TAx5xxx | 199mV [-20dBr] | -96 | -95 | -95 |

| ADC6120 | 199mV [-20dBr] | -91 | -91 | -97 |

| ADC6120-DRE | 199mV [-20dBr] | -91 | -91 | -97 |