SLVUCG9 October 2022 TPS36-Q1

3.3 Layout and Component Placement

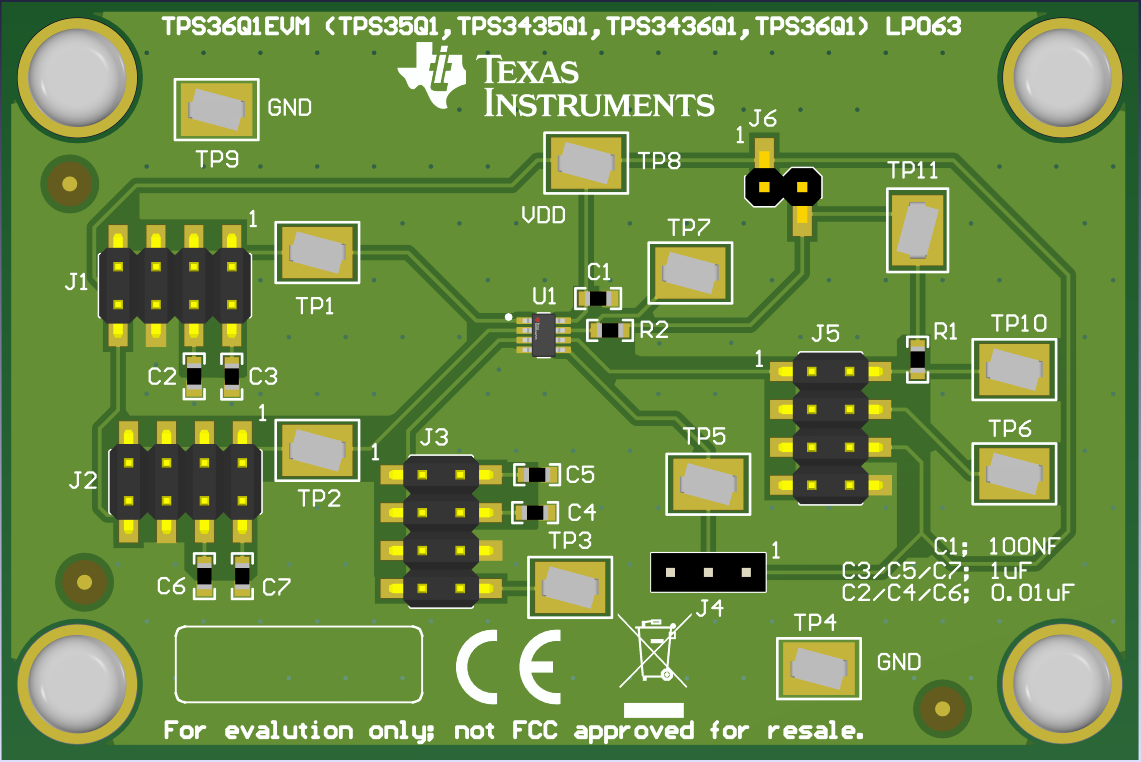

Figure 3-2 and Figure 3-3 show the top and bottom assemblies of the printed circuit board (PCB) to show the component placement on the EVM.

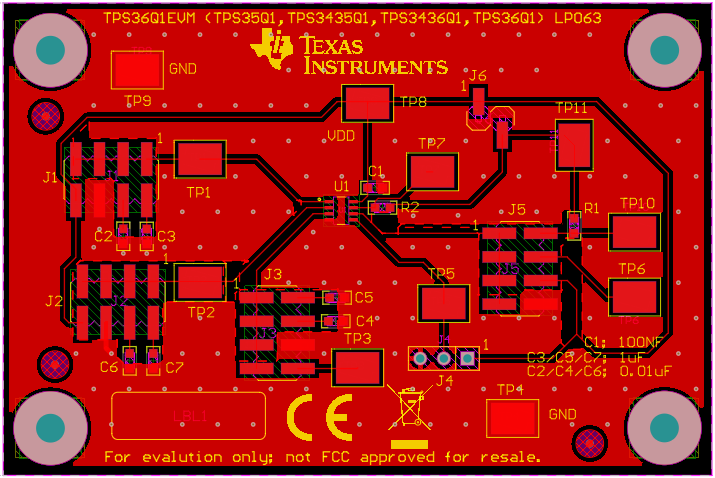

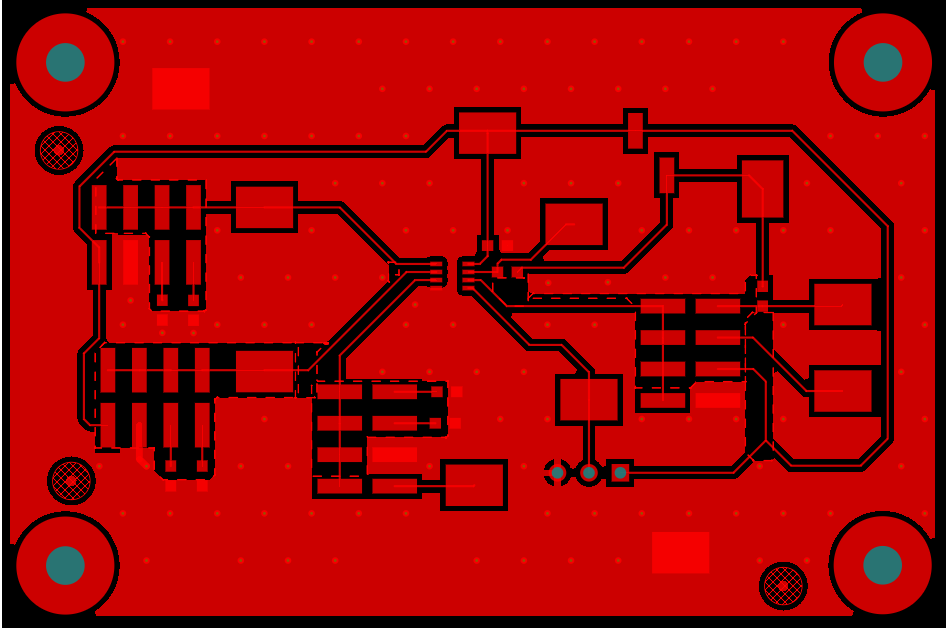

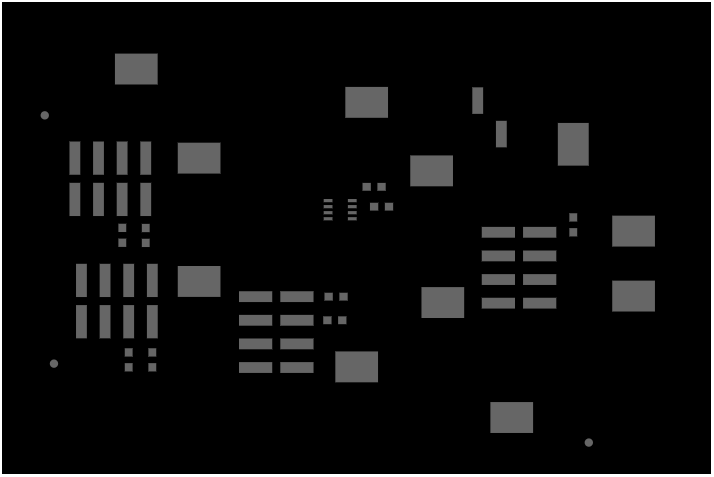

Figure 3-4 and Figure 3-5 show the top and bottom layouts, Figure 3-6 and Figure 3-7 show the top and bottom layers, and Figure 3-8 shows the top solder mask of the EVM.

Figure 3-2 Component Placement—Top

Assembly

Figure 3-2 Component Placement—Top

Assembly Figure 3-4 Layout—Top

Figure 3-4 Layout—Top Figure 3-6 Top Layer

Figure 3-6 Top Layer Figure 3-8 Top Solder Mask

Figure 3-8 Top Solder Mask Figure 3-3 Component Placement—Bottom

Assembly

Figure 3-3 Component Placement—Bottom

Assembly Figure 3-5 Layout—Bottom

Figure 3-5 Layout—Bottom Figure 3-7 Bottom Layer

Figure 3-7 Bottom Layer