SLVUCQ6 july 2023 TPS7H2211-SEP

3.2 Parallel Configuration Results

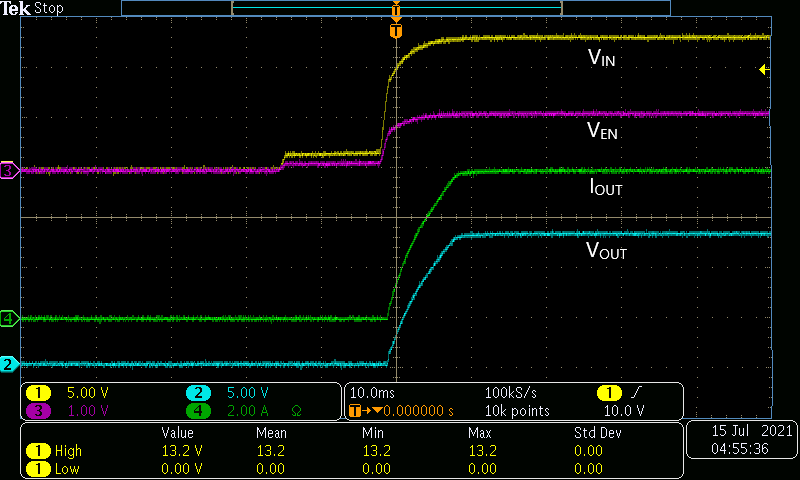

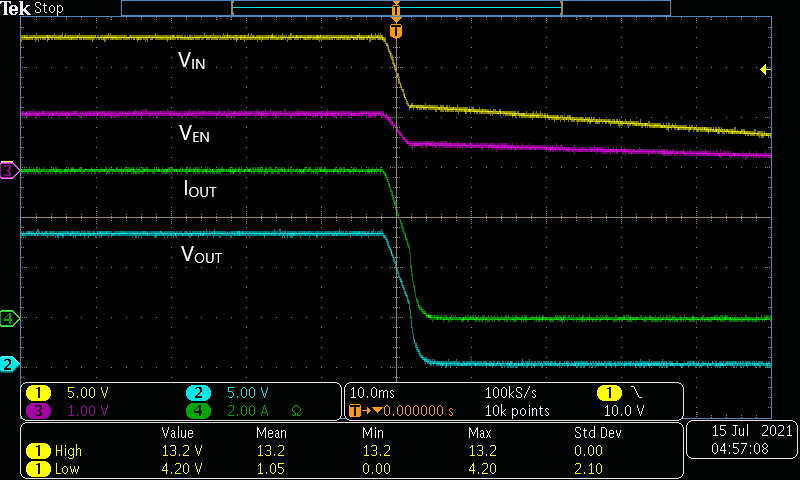

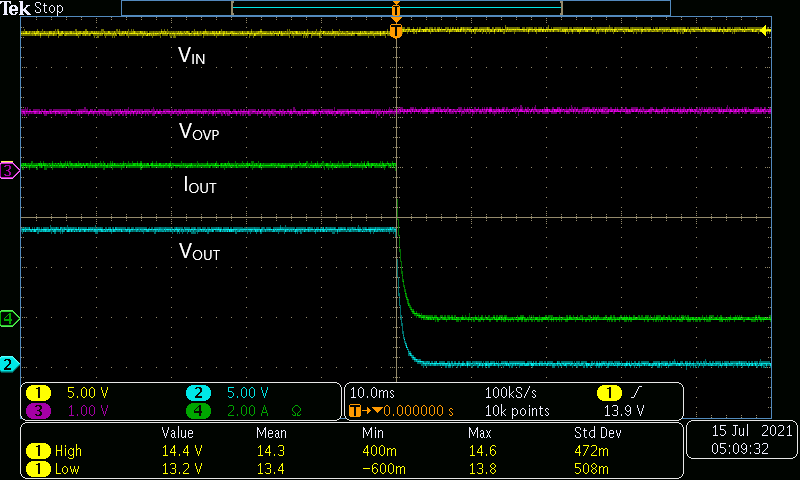

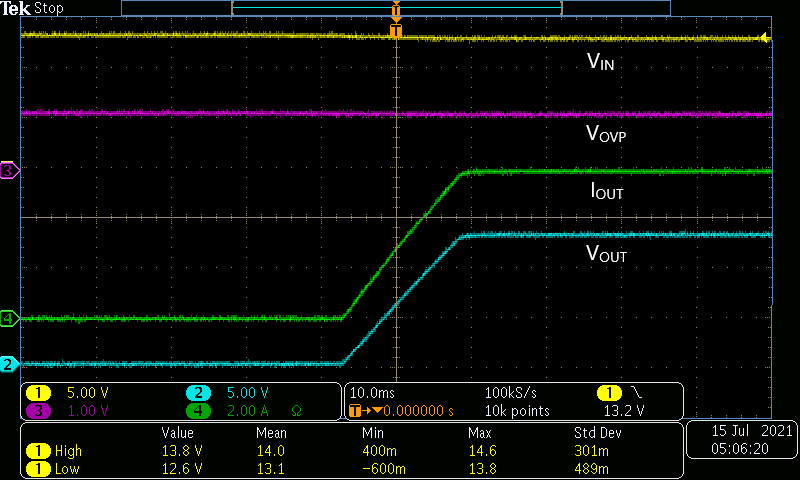

The results shown in Figure 4-5 through Figure 4-8 were observed using the TPS7H2211EVM in the parallel configuration shown in this document with VIN = 13 V.

Figure 3-5 Parallel Configuration: Start Up

Figure 3-5 Parallel Configuration: Start Up Figure 3-6 Parallel Configuration: Shutdown

Figure 3-6 Parallel Configuration: Shutdown Figure 3-7 Parallel Configuration: Assertion of OVP due to Input Voltage

Figure 3-7 Parallel Configuration: Assertion of OVP due to Input Voltage Figure 3-8 Parallel Configuration: Deassertion of OVP due to Input Voltage

Figure 3-8 Parallel Configuration: Deassertion of OVP due to Input Voltage