SNAU296 December 2023 LMK5C33414A

- 1

- Abstract

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM

Schematics

- 4.1 Power Supply Schematic

- 4.2 Alternative Power Supply Schematic

- 4.3 Power Distribution Schematic

- 4.4 LMK5C33414A and Input References IN0 to IN3 Schematic

- 4.5 Clock Outputs OUT0 to OUT3 Schematic

- 4.6 Clock Outputs OUT4 to OUT9 Schematic

- 4.7 Clock Outputs OUT10 to OUT13 and Clock Inputs IN2 and IN3 Schematic

- 4.8 XO Schematic

- 4.9 Logic I/O Interfaces Schematic

- 4.10 USB2ANY Schematic

- 5EVM Bill of Materials

-

6Appendix A - TICS Pro LMK5C33414A Software

- 6.1 Using the Start Page

- 6.2 Using the Status Page

- 6.3 Using the Input Page

- 6.4 Using APLL1, APLL2, and APLL3 Pages

- 6.5 Using the DPLL1, DPLL2, and DPLL3 Pages

- 6.6 Using the Validation Page

- 6.7 Using the GPIO Page

- 6.8 SYNC/SYSREF/1-PPS Page

- 6.9 Using the Outputs Page

- 6.10 EEPROM Page

- 6.11 Design Report Page

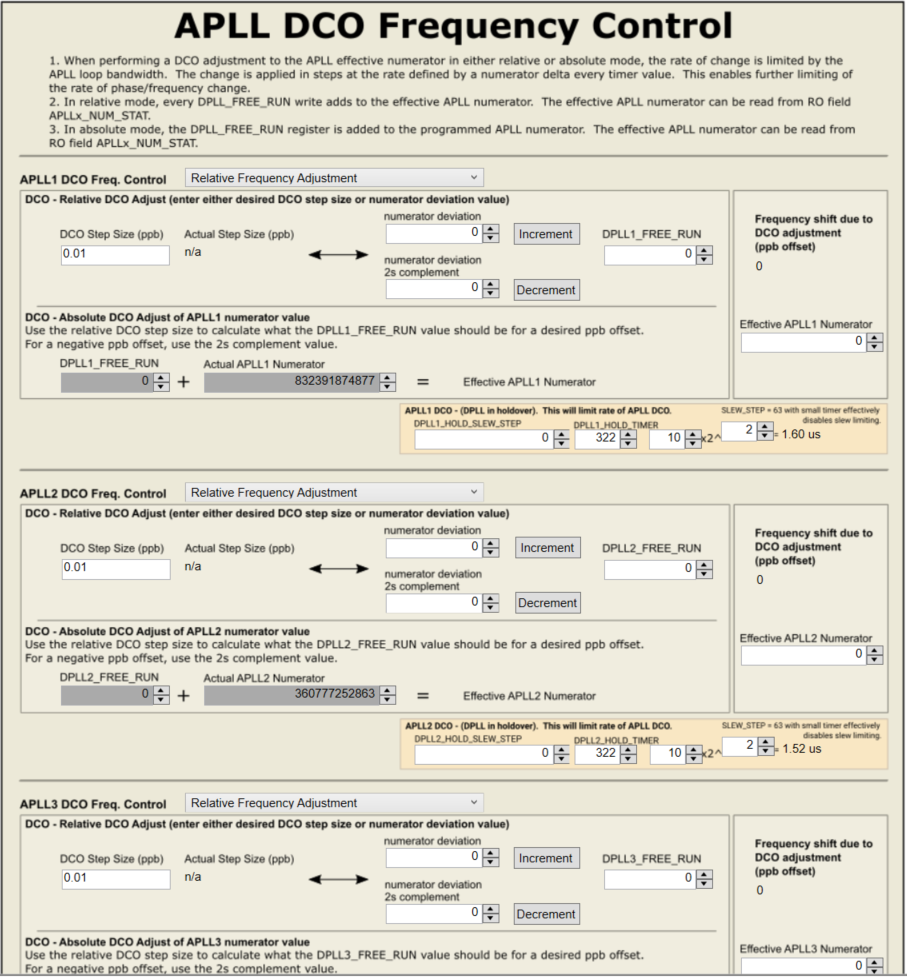

6.4.1 APLL DCO

To use the DCO shift controls on a given APLL, enter the DCO ppb step value into the DCO Step Size (ppb) box shown below. The entered step size is used to calculate a numerator deviation and a 2 s complement numerator deviation. To perform the shift, the increment or decrement button must be pressed. An increment writes the numerator deviation to the DPLLx_FREE_RUN control, which results in a positive frequency shift in the amount specified by the DCO Step Size (ppb). An decrement writes the 2 s complement numerator deviation to the DPLLx_FREE_RUN control, which results in a negative frequency shift in the amount specified by the DCO Step Size (ppb).

The slew rate at which the adjustment occurs is set on the DPLLx_HOLD_SLEW_STEP control. Make sure the DPLLx_HOLD_SLEW_STEP is NOT equal to 0, otherwise the adjustment does not occur. The recommended DPLLx_HOLD_SLEW_STEP value is 63 (maximum value). A value of 63 results in the fastest adjustment.

Figure 6-16 APLL DCO Controls

Figure 6-16 APLL DCO Controls