SNOA961A February 2017 – February 2023 LDC2112 , LDC2114 , LDC3114 , LDC3114-Q1

- Inductive Touch System Design Guide for HMI Button Applications

- 1Mechanical Design

- 2Sensor Design

- 3Summary

- 4Revision History

2.4.6.1 Sensor Parasitic Capacitance

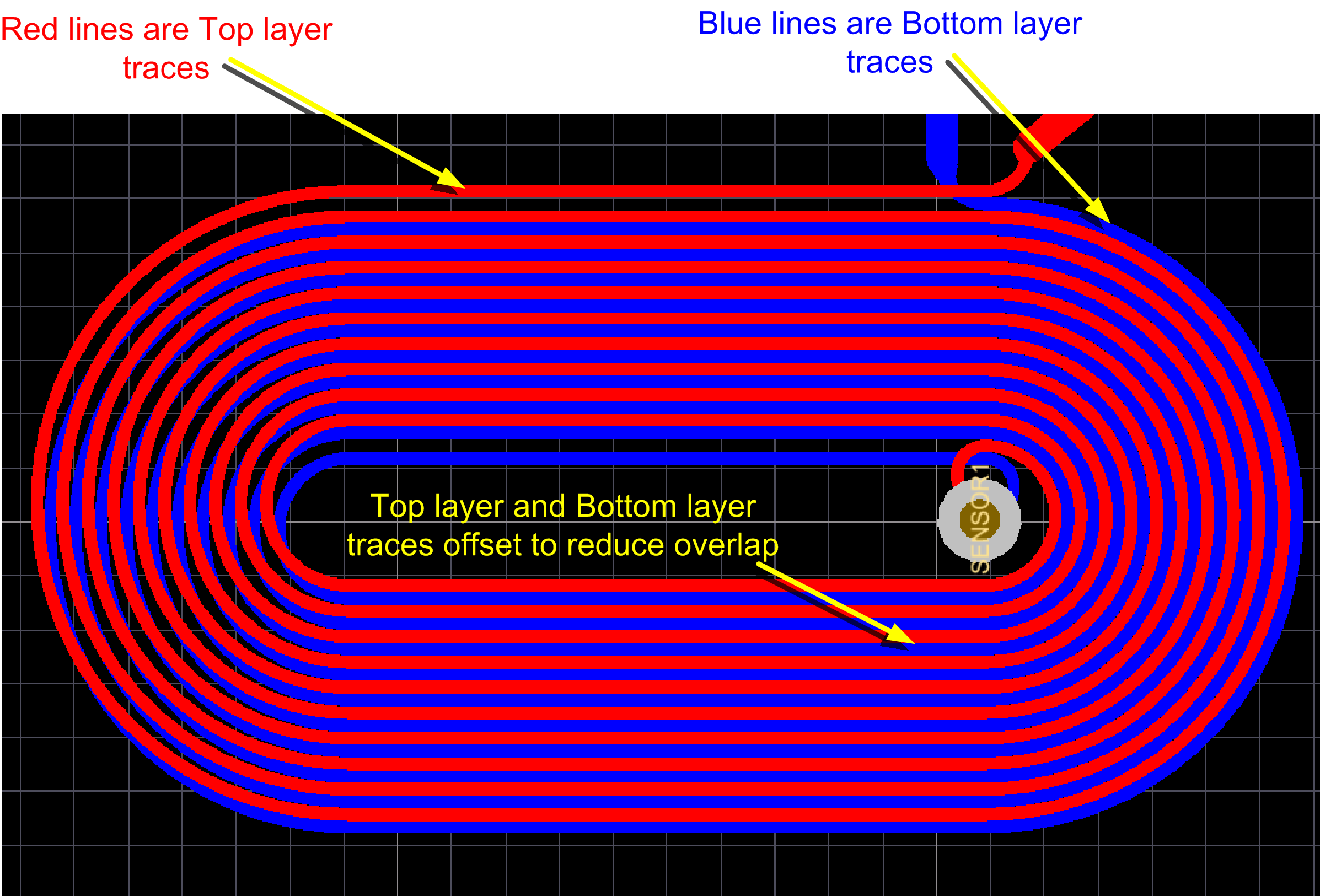

The individual turns of an inductor have a physical area and are separated by a dielectric, which manifests as small parasitic capacitor across each turn. These parasitic capacitances should be minimized for optimum sensor performance. One simple but effective technique for multi-layer sensors to reduce the parasitic capacitance is to offset any parallel traces between layers, as shown in #T4726003-70.

Figure 2-9 Offsetting Traces to Reduce Parasitic Capacitance

Figure 2-9 Offsetting Traces to Reduce Parasitic Capacitance