SNVA453B August 2011 – January 2022 LM10500

- Trademarks

- 1 LM10500 Overview

- 2 Adaptive Voltage Scaling Technology

- 3 Features

- 4 Applications

- 5 Evaluation Kit Overview

- 6 Typical Application Circuit

- 7 Connection Guide

- 8 Operation Guide

- 9 User’s GUI for LM10500 Evaluation Board

- 10Typical Performance Characteristics

- 11Evaluation Board Schematic

- 12Evaluation Board Bill of Materials

- 13Evaluation Board Layout

- 14Revision History

9.2 GUI Layout and Conventions

Buttons in their depressed position mean that the corresponding bits are equal to 1, logic high, and in the raised position show the corresponding bits are equal to 0, logic low. '-0-' on a button means the bit is not used. Reading from unused bits returns '0' and writing to unused bits are ignored.

The top four lines of the GUI are the PWI registers of the LM10500. R0 controls the core voltage, ranging from 00h to 7Fh. R4 shows the PWI version: 01h means PWI1.0 and 02h means PWI2.0. R9 is the core voltage offset and the default value differs in LM10500SQ-0.8 and LM10500SQ-1.0. The default value of R9 is 00h in LM10500SQ-1.0 and 40h in LM10500SQ-0.8. The actual core voltage code is determined by the resulting code of (R0-R9) if (R0-R9) is above zero, otherwise, the core voltage code is zero. R10 enables and disables FPWM and stepping controls. Please refer to the LM10500 5A Step-Down Energy Management Unit w/PowerWise Adaptive Voltage Scaling data sheet for more details.

The ‘ENABLE’ button controls the hardware enable if it is connected to LM10500.

The PWROK and Auth_OK are read-only bits, indicating the LM10500 has proper output voltage and successful authentication, respectively.

The PWI commands buttons send out commands to alter the operating state of the PWI secondary: the LM10500, authenticate and synchronize. Please refer to PowerWise interface specification for the details of PWI standard at pwistandard.com.

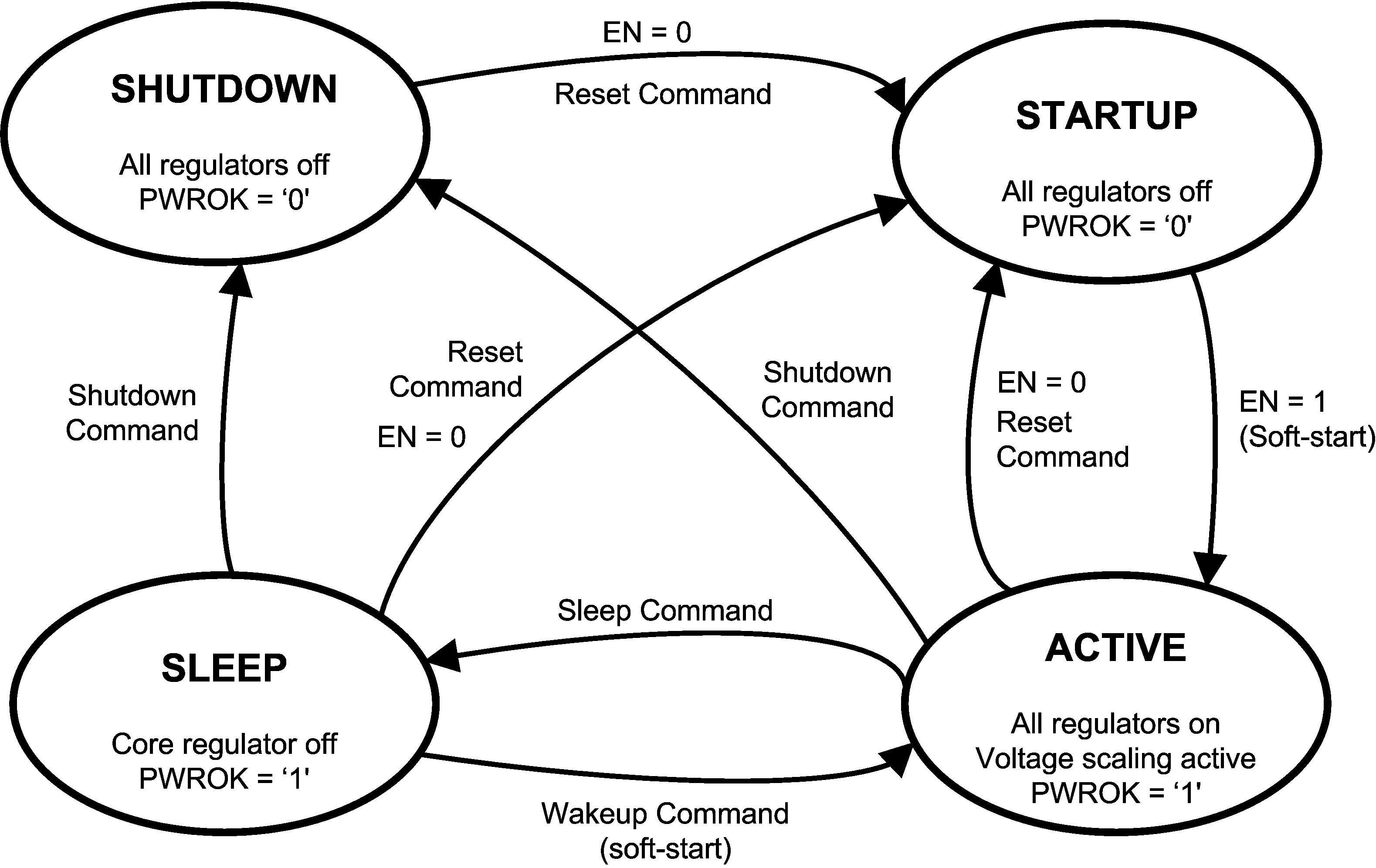

A summary of the operation state is shown in Figure 9-3.

Figure 9-3 PWI Secondary Operation States Diagram

Figure 9-3 PWI Secondary Operation States Diagram