SPRACN0F October 2021 – March 2023 F29H850TU , F29H859TU-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- The Essential Guide for Developing With C2000™ Real-Time Microcontrollers

- Trademarks

- 1C2000 and Real-Time Control

-

2Sensing Key Technologies

- 2.1 Accurate Digital Domain Representation of Analog Signals

- 2.2 Optimizing Acquisition Time vs Circuit Complexity for Analog Inputs

- 2.3 Hardware Based Monitoring of Dual-Thresholds Using a Single Pin Reference

- 2.4 Resolving Tolerance and Aging Effects During ADC Sampling

- 2.5 Realizing Rotary Sensing Solutions Using C2000 Configurable Logic Block

- 2.6 Smart Sensing Across An Isolation Boundary

- 2.7 Enabling Intra-Period Updates in High Bandwidth Control Topologies

- 2.8 Accurate Monitoring of Real-Time Control System Events Without the Need for Signal Conditioning

-

3Processing Key Technologies

- 3.1 Accelerated Trigonometric Math Functions

- 3.2 Fast Onboard Integer Division

- 3.3 Hardware Support for Double-Precision Floating-Point Operations

- 3.4 Increasing Control Loop Bandwidth With An Independent Processing Unit

- 3.5 Flexible System Interconnect: C2000 X-Bar

- 3.6 Improving Control Performance With Nonlinear PID Control

- 3.7 Understanding Flash Memory Performance In Real-Time Control Applications

- 3.8 Deterministic Program Execution With the C28x DSP Core

- 3.9 Efficient Live Firmware Updates (LFU) and Firmware Over-The-Air (FOTA) updates

-

4Control Key Technologies

- 4.1 Reducing Limit Cycling in Control Systems With C2000 HRPWMs

- 4.2 Shoot Through Prevention for Current Control Topologies With Configurable Deadband

- 4.3 On-Chip Hardware Customization Using the C2000 Configurable Logic Block

- 4.4 Fast Detection of Over and Under Currents and Voltages

- 4.5 Improving System Power Density With High Resolution Phase Control

- 4.6 Safe and Optimized PWM Updates in High-Frequency, Multi-Phase and Variable Frequency Topologies

- 4.7 Solving Event Synchronization Across Multiple Controllers in Decentralized Control Systems

- 5Interface Key Technologies

- 6Safety Key Technologies

- 7References

- 8Revision History

3.6.2 In Depth

Conventional linear controllers such as the Proportional, Integral, Derivative (PID) are widely used with digital power applications, including motor control and motion control. The nonlinear PID (DCL Training Video - Non-linear Control) provided with the DCL extends the performance of its linear counterpart by shaping the loop error using a nonlinear law. A nonlinear shaping block is introduced in series with each of the three controller paths as shown below.

Figure 3-10 Non-Linear PID Block

Diagram

Figure 3-10 Non-Linear PID Block

DiagramThe shape and aggressiveness of nonlinear action are configurable via six additional controller parameters (two in each nonlinear block), which are typically tuned in an iterative fashion to optimize a transient response. Like other controllers in the DCL, the NLPID parameters can be updated safely using a shadow parameter set and an update function.

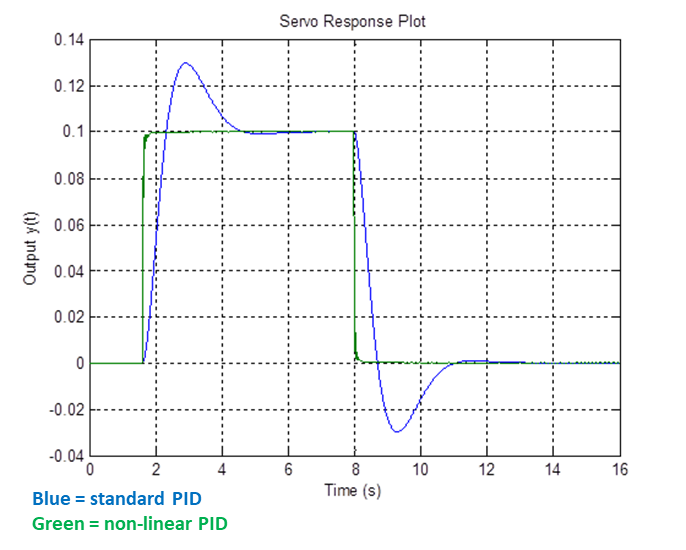

#T5843526-264 shows an example of the potential improvement in step response available from the use of nonlinear control action.

Figure 3-11 Comparison of Response Time

Between Linear and Non-linear PID

Figure 3-11 Comparison of Response Time

Between Linear and Non-linear PIDThe NLPID executes with highest efficiency on devices equipped with the type 1 TMU (see GUID-5E5EBF43-A78B-40F9-B8A7-51DB8C80D65E.html#GUID-5E5EBF43-A78B-40F9-B8A7-51DB8C80D65E), such as the F280025 device. These devices have CPU instructions that allow the nonlinear controller to be executed in 117 cycles compared with around 3,300 cycles without such instructions. This cycle efficiency allows the nonlinear PID to be used in high frequency applications such as switching power supplies and current control loops.

The DCL is packaged in C2000Ware, which is available for free download by C2000 users. The library includes a PID controller tuning guide to help users get the most from the NLPID controller.