SPRUJ85A April 2024 – August 2024

PRODUCTION DATA

- 1

- Description

- 1Key Features

- 2LaunchPad Module Overview

-

3Hardware Description

- 4.1 Board Setup

- 4.2 Functional Block Diagram

- 4.3 GPIO Mapping

- 4.4 Reset

- 4.5 Clock

- 4.6 Memory Interfaces

- 4.7 Ethernet Interface

- 4.8 I2C

- 4.9 Industrial Application LEDs

- 4.10 SPI

- 4.11 UART

- 4.12 MCAN

- 4.13 FSI

- 4.14 JTAG

- 4.15 TIVA and Test Automation Header

- 4.16 LIN

- 4.17 ADC and DAC

- 4.18 EQEP and SDFM

- 4.19 EPWM

- 4.20 BoosterPack Headers

- 4.21 Pinmux Mapping

- 4Additional Information

- 5References

- 6Revision History

3.20 BoosterPack Headers

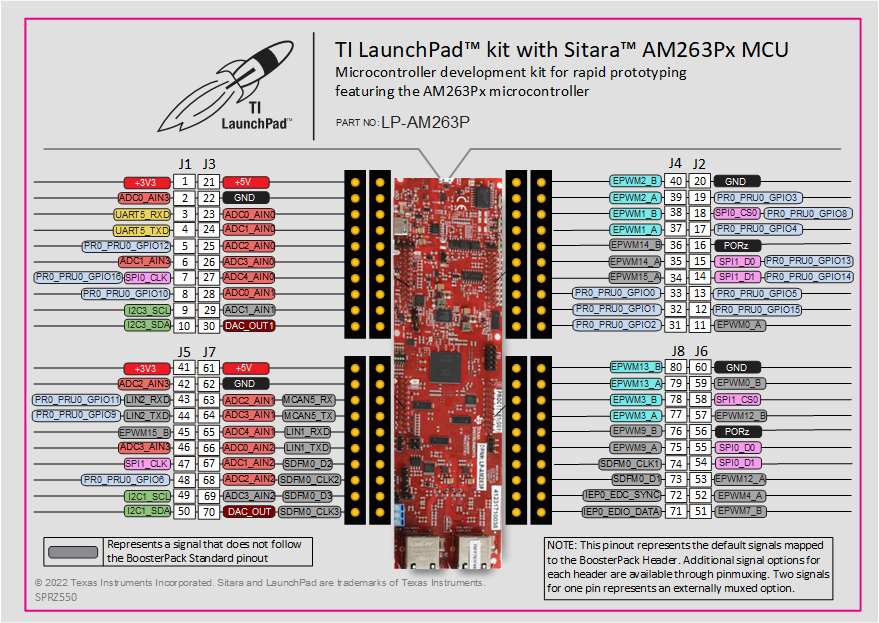

Figure 3-31 AM263Px LaunchPad BoosterPack Pinout

Figure 3-31 AM263Px LaunchPad BoosterPack PinoutNote: This pinout represents the default signals mapped to the BoosterPack Header. Additional signal options for each header are available through Pinmux Mapping. Two signals for one pin represents an externally muxed option

The AM263Px LaunchPad supports two fully independent BoosterPack XL connectors. BoosterPack site #1 (J1/J3, J2/J4) is located in between the SoC and the micro-B USB Connector. BoosterPack site #2 (J5/J7, J6/J8) is located in between the SoC and the RJ45 connectors. Each GPIO has multiple functions available through the GPIO mux. The signals connected from the SoC to the BoosterPack headers include:

- Various ADC inputs

- DAC outouts

- UART5

- Various GPIO signals

- SPI0 and SPI1

- I2C1 and I2C3

- Various EPWM channels

- LIN1 and LIN2

- MCAN1

- SDFM0