SPRUJ91A april 2023 – may 2023 AM68 , AM68 , AM68A , AM68A , TDA4AL-Q1 , TDA4AL-Q1 , TDA4VE-Q1 , TDA4VE-Q1 , TDA4VL-Q1 , TDA4VL-Q1

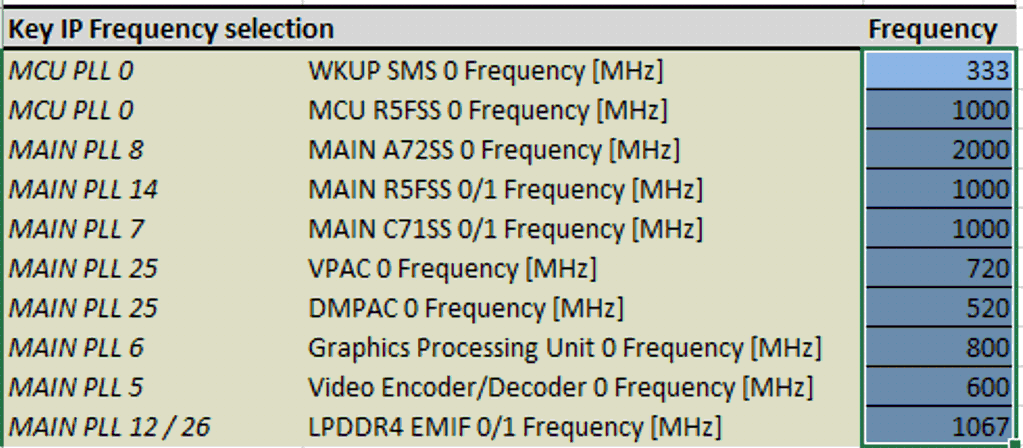

3.2 Key IP Frequency Selection

This block allows the user to select the frequency for the key blocks in the core utilization block (+DDR).

Note: VPAC / DMPAC – An important note on PLL25. Since the

internal frequency of the PLL is limited to -3 GHz, the VPAC and DMPAC cannot

simultaneously run at the highest frequency (720 MHz and 520 MHz, respectively) for

both IPs.