SWRA640H December 2018 – May 2024 CC1310 , CC1312R , CC1314R10 , CC1350 , CC1352P , CC1352R , CC1354P10 , CC1354R10 , CC2620 , CC2630 , CC2640 , CC2640R2F , CC2640R2F-Q1 , CC2642R , CC2642R-Q1 , CC2650 , CC2652P , CC2652R , CC2652R7 , CC2652RB , CC2652RSIP , CC2674P10 , CC2674R10

- 1

- Abstract

- Trademarks

- 1 Reference Design

- 2 Front-End Configurations

- 3 Schematic

- 4 PCB Layout

- 5 Antenna

- 6 Crystal Tuning

- 7 TCXO Support

- 8 Integrated Passive Component (IPC)

- 9 Optimum Load Impedance

- 10PA Table

- 11Power Supply Configuration

- 12Board Bring-Up

- 13References

- 14Revision History

11.3 Global LDO Mode

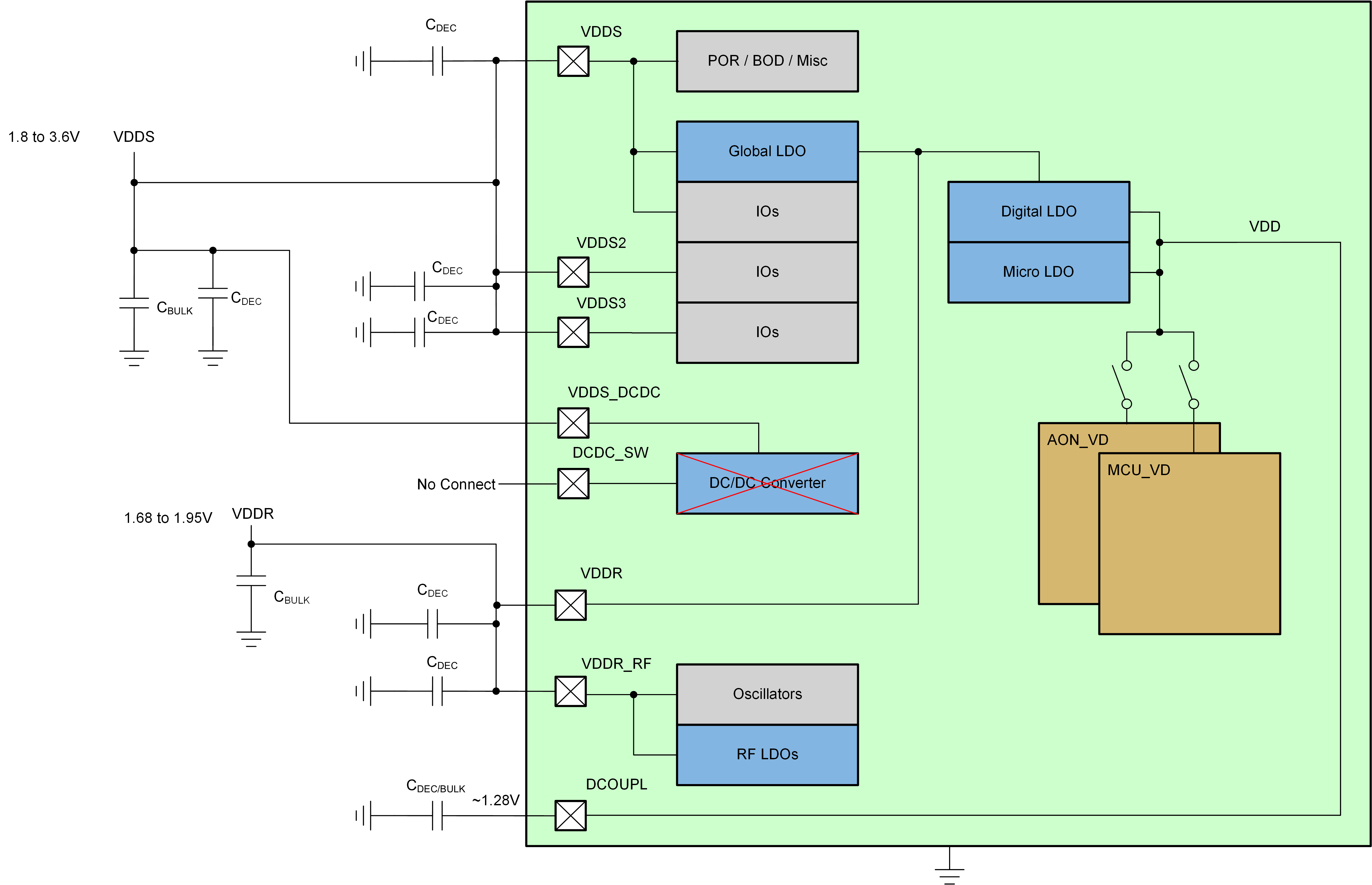

Figure 11-2 Global LDO Mode

Figure 11-2 Global LDO ModeTo save cost and PCB area the DC/DC inductor can be removed and VDDR can be supplied from the Global LDO at the cost of higher power consumption. In this mode a bulk capacitor on VDDR is still required and should be placed close to the VDDR pin. The VDDS_DCDC-pin must be connected to VDDS and the DCDC_SW should be left floating to avoid short circuiting VDDS if the DC/DC converter is mistakenly enabled from software. The VDDS bulk capacitor does not need to be close to the VDDS_DCDC pin and should rather be placed close to the VDDS pin.

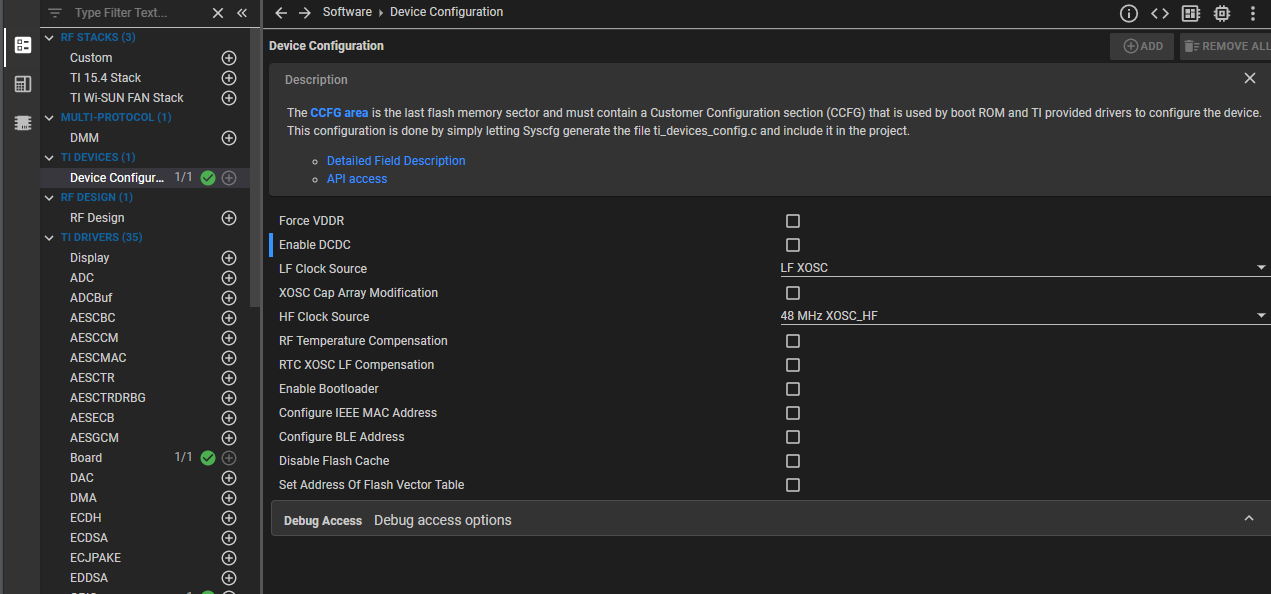

The software setup required to use the DCDC converter or the GLDO operation is done in the Customer Configuration (CCFG) register bank.

For devices that use SDK up to version 5.x (CC2640R2), the settings below must be made to the file ccfg.c.

#ifndef SET_CCFG_MODE_CONF_DCDC_RECHARGE

// #define SET_CCFG_MODE_CONF_DCDC_RECHARGE 0x0 // Use the DC/DC during recharge in powerdown

#define SET_CCFG_MODE_CONF_DCDC_RECHARGE 0x1 // Do not use the DC/DC during recharge in powerdown

#endif

#ifndef SET_CCFG_MODE_CONF_DCDC_ACTIVE

// #define SET_CCFG_MODE_CONF_DCDC_ACTIVE 0x0 // Use the DC/DC during active mode

#define SET_CCFG_MODE_CONF_DCDC_ACTIVE 0x1 // Do not use the DC/DC during active mode

#endifFor devices that use SDK version 6.x and above, this is set up in the section TI DEVICES followed by Device Configuration of the Sysconfig file as indicated in the following image.