SWRA779 September 2023 CC3300 , CC3301

3.3.3 SPI Flow Control

Unlike SDIO, SPI interface does not include a built-in flow control mechanism. One option is to add a hardware pin to indicate that the slave device is ready or not ready to receive data from the host controller. Another option is to implement a proprietary in-band protocol that uses the SPI data lines in form of dedicated commands or other signaling method.

CC33xx companion IC implements a peripheral to host controller flow control, meaning the peripheral may indicate to the host controller to stop transmission. This is done using the POCI data line by indicating a busy signal. This method is also used for autonomous mode implementation to indicate when the peripheral is ready and when it is not ready.

A busy signal is reflected by ‘0’ value bit stream. The host controller is expected to ignore the busy signal on the POCI line, until there is at least one bit with the value '1' ending a word. The stream of ‘1’ would be referred as ~busy signal. The word size is well defined and is part of the configuration phase. The word size can be either 16 bits or 32 bits. The first data word will be the first word following the word containing the ~busy signal. Data endianity is disregarded and does not make a difference.

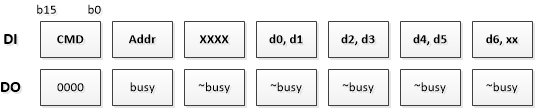

Figure 3-1 illustrates 16-bit data in Big Endian format (least significant byte is on the wire first) in write direction.

Figure 3-1 16 Bits, Big Endian, Write

Direction

Figure 3-1 16 Bits, Big Endian, Write

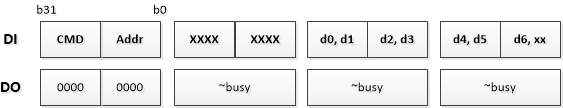

DirectionFigure 3-2 illustrates 32-bit data in Big Endian format (most significant byte is on the wire first) in write direction.

Figure 3-2 32 Bits, Big Endian, Write

Direction

Figure 3-2 32 Bits, Big Endian, Write

DirectionCC33xx companion IC also implements a peripheral to host controller flow control in read direction, meaning the peripheral may indicate to the host controller to stop reception (or when to start reception). It works similarly to the write direction.

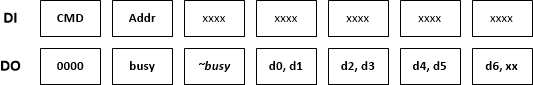

Figure 3-3 illustrates 16-bit data in Big Endian format (i.e. least significant byte is on the wire first) in read direction.

Figure 3-3 16 Bits, Big Endian, Read

Direction

Figure 3-3 16 Bits, Big Endian, Read

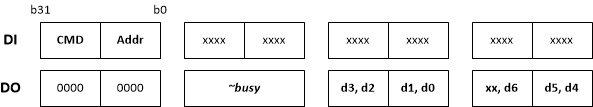

DirectionFigure 3-4 illustrates 32-bit data in Little Endian format (i.e. most significant byte is on the wire first) in read direction.

Figure 3-4 32 Bits, Big Endian, Read

Direction

Figure 3-4 32 Bits, Big Endian, Read

Direction