-

OPAx202 重い容量性負荷を駆動できる高精度、低ノイズ 36V オペアンプ

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

- 重要なお知らせ

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

DATA SHEET

OPAx202 重い容量性負荷を駆動できる高精度、低ノイズ 36V オペアンプ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 高精度のスーパーベータ性能

- 低オフセット電圧:200µV (最大値)

- 超低ドリフト:1µV/℃ (最大値)

- 優れた効率

- 静止電流:580µA (標準値)

- ゲイン帯域幅積:1MHz

- 低入力電圧ノイズ:9nV/√Hz

- 使いやすく、設計がシンプル

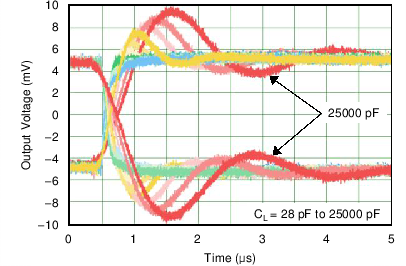

- 重い容量性負荷の駆動:25nF で 5µs のセトリング時間

- 極めて高い入力インピーダンス:3000GΩ および

0.5pF - EMI 強化、熱、短絡保護

- 安定した性能

- 高い CMRR と AOL:126dB (最小値)

- 高い PSRR:126dB (最小値)

- 低バイアス電流:2nA (最大値)

- 低ノイズ:0.2µVPP (0.1Hz~10Hz)

- 広い電源電圧範囲:±2.25V~±18V

- OP-07およびOP-27の置き換え

3 概要

OPA202、OPA2202、OPA4202 (OPAx202) は、TI の業界最先端の高精度スーパーベータ相補性バイポーラ半導体プロセスで製造されたデバイス・ファミリです。このプロセスを使用すると、非常に低いフリッカー・ノイズ、低いオフセット電圧、低いオフセット電圧温度ドリフト、同相と電源変動に対する非常に優れた直線性が得られます。これらのデバイスは、DC 精度、重い容量性負荷の駆動、外部 EMI、熱、短絡に対する保護において非常に優れています。

消費電流は ±18V で 580µA です。OPAx202 は位相反転を起こさず、大きな容量性負荷でも安定に動作します。OPAx202 は、-40℃~+105℃の温度範囲で完全に動作が規定されています。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| OPA202 | SOIC (8) | 4.90mm×3.91mm |

| SOT-23 (5) | 2.90mm×1.60mm | |

| VSSOP (8) (プレビュー) | 3.00mm × 3.00mm | |

| OPA2202 | VSSOP (8) | 3.00mm×3.00mm |

| OPA4202 | SOIC (14) | 8.65mm×3.91mm |

- 利用可能なすべてのパッケージについては、このデータシートの末尾にあるパッケージ・オプションについての付録を参照してください。

OPAx202 は大きな容量性負荷を直接駆動しても優れた性能を発揮

4 改訂履歴

Changes from D Revision (December 2019) to E Revision

- Added OPA202 の 8 ピン VSSOP (DGK) プレビュー・パッケージおよび関連情報をデータシートにGo

Changes from C Revision (October 2018) to D Revision

- Changed OPA2202 および OPA4202 を事前情報 (プレビュー) から量産データ (アクティブ) にGo

Changes from B Revision (December 2018) to C Revision

- Added OPA2202 および OPA4202 プレビュー・デバイスおよび関連情報をデータシートにGo

- Deleted Operating Voltage section; redundant informationGo

Changes from A Revision (September 2018) to B Revision

- Changed SOT-23 パッケージをプレビューから量産データにGo

Changes from * Revision (October 2017) to A Revision

- Added SOT-23 パッケージのプレビュー情報をGo