-

SNx5ALS180 差動ドライバとレシーバのペア JAJSPG9H August 1987 – January 2023 SN65ALS180 , SN75ALS180

PRODUCTION DATA

-

SNx5ALS180 差動ドライバとレシーバのペア

- 1 特長

- 2 概要

- 3 Revision History

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Thermal Information

- 5.4 Electrical Characteristics - Driver

- 5.5 Switching Characteristics - Driver

- 5.6 Symbol Equivalents

- 5.7 Electrical Characteristics - Receivers

- 5.8 Switching Characteristics - Receivers

- 5.9 Typical Characteristics

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

- 重要なお知らせ

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|14

サーマルパッド・メカニカル・データ

発注情報

DATA SHEET

SNx5ALS180 差動ドライバとレシーバのペア

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- TIA/EIA-422-B、TIA/EIA-485-A の要件を満たしているか、それを上回っています。(1) ITU 勧告 V.11 です。

- 高速の高度な低消費電力ショットキー回路

- シリアルとパラレルの両方のアプリケーションでの 25Mbaud 動作に対応

- デバイス間の低スキュー:6ns (最大)

- 小さい消費電流要件:30mA 以下

- デュアル VCC およびデュアル GND を備えた個別のドライバおよびレシーバ I/O ピン

- 広い正および負の入力 / 出力バス電圧範囲

- ドライバ出力能力:±60mA

- サーマル・シャットダウン保護機能

- ドライバの正および負の電流制限

- レシーバ入力インピーダンス:12kΩ 以上

- レシーバ入力感度:最大 ±200mV

- レシーバ入力ヒステリシス:60mV (標準値)

- 単一の 5V 電源で動作

- グリッチ・フリーのパワーアップ / パワーダウン保護機能

1. これらのデバイスは、ジェネレータ競合テスト (3.4.2 項) とジェネレータ電流制限 (3.4.3 項) を除き、TIA/EIA-485-A の要件を満たしているか、それを上回っています。適用されるテスト電圧範囲は、SN75ALS180 では -6V~8V、SN65ALS180 では -4V~8V で、

2 概要

SN65ALS180 および SN75ALS180 差動ドライバおよびレシーバのペアは、マルチポイント・バス伝送ラインでの双方向データ通信用に設計された IC です。これらのデバイスは平衡伝送ライン用に設計されており、TIA/EIA-422-B、TIA/EIA-485-A、ITU 勧告 V.11 を満たしています。

SN65ALS180 および SN75ALS180 は、3 ステート差動ライン・ドライバと差動入力ライン・レシーバを統合しており、どちらも 5V 単一電源で動作します。ドライバとレシーバはそれぞれアクティブ High、アクティブ Low のイネーブルを備えており、それらのイネーブルを外部で互いに接続することで、方向制御として機能させることができます。ドライバの差動出力とレシーバの差動入力は、自由度が増すように個別の端子に接続されており、ドライバがディセーブルされた場合、または VCC = 0 の場合、バスへの負荷が最小化されるように設計されています。

これらのポートは広い正および負の同相モード電圧範囲を持っているため、本デバイスはパーティライン・アプリケーションに適しています。

パッケージ情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| SNx5ALS176 | D (SOIC) | 8.65mm × 3.91mm |

| N (PDIP) | 19.3mm × 6.35mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

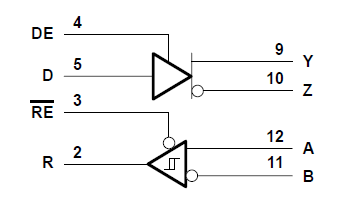

論理図 (正論理)

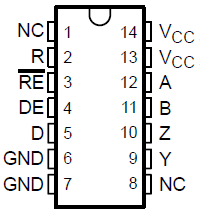

論理図 (正論理)4 Pin Configuration and Functions

NC – No internal connection

Figure 4-1 SN65ALS180 D PackageSN75ALS180 D or N Package

(Top View)

Table 4-1 Pin Functions

| NO | Name | Type | Description |

|---|---|---|---|

| 1 | NC | - | No Internal connection |

| 2 | R | O | Receive data output |

| 3 | RE | I | Receiver enable, active low |

| 4 | DE | I | Driver enable, active high |

| 5 | D | I | Driver data input |

| 6, 7 | GND | GND | Device ground |

| 8 | NC | - | No Internal connection |

| 9 | Y | O | Digital bus output, Y (Complementary to Z) |

| 10 | Z | O | Digital bus output, Z (Complementary to Y) |

| 11 | A | I | Bus input, A (complementary to B) |

| 12 | B | I | Bus input, B (complementary to A) |

| 13, 14 | VCC | SUPPLY | 4.75V to 5.25V supply |