-

高精度 ADC への電力供給:平均電流と過渡電流の比較

1 はじめに

A/D コンバータ (ADC) のデータシートに掲載されている電源パラメータを理解すると、より信頼性の高い高精度データ アクイジション (DAQ) システムを設計できます。特に、ADC データシートの消費電流は、定常状態の動作条件で規定された平均値であることを理解することが重要です。したがって、ADC の過渡電流が規定の ADC 電流より数桁大きくなる可能性があるとしても、これらの測定電流値は過渡電流要求の特性を示すものではありません。過渡電流は、異なる ADC 動作モード間の遷移中に発生する可能性があり、デバイスへの最初の電力供給時に最も大きくなります。さらに、ADC を取り囲む回路と部品が原因で、更に大きな過渡電流要求が発生する可能性があります。

この記事では、ADC の過渡電流要件について詳細に説明します。先ず最初に、代表的な ADC のデータシートが電流をどのように規定しているかを紹介し、次に、さまざまな動作条件下で過渡電流要求を定量化するいくつかのテストの結果を示します。さらに、平均電流と過渡電流の両方を供給できる複数の電源構成について説明し、最後にさまざまなパワーダウン方式が及ぼす影響を比較します。

2 電源の仕様

ADC のデータシートに記載されている消費電流は、定常状態の動作条件で規定された平均値です。さまざまな動作条件を持つ ADC では、いくつかの電流値の仕様が必要です。これらの条件には、データ レートに対してスケーリングされる平均 ADC 電源電流、またはプログラマブル ゲイン アンプ (PGA) や電圧リファレンス (VREF) などの内部機能をイネーブルにしたときの、電流需要の増加を含めることができます。たとえば、表 1 に PGA と VREF を内蔵した 24 ビット、40kSPS、11 チャネルのデルタ シグマ ADC であるテキサス・インスツルメンツの ADS1261 の、さまざまな動作条件でのデータシート記載の電源仕様を示します。

| 電源 | ||||||

|---|---|---|---|---|---|---|

| パラメータ | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 | |

| IAVVD、IAVSS | アナログ電源電流 | PGA バイパス | 2.7 | 4.5 | mA | |

| PGA モード、ゲイン = 1 ~ 32 | 3.8 | 6 | ||||

| PGA モード、ゲイン = 64 または 128 | 4.3 | 6.5 | ||||

| パワーダウン・モード | 2 | 8 | μA | |||

| IAVVD、IAVSS | アナログ電源電流 (機能別) | 電圧リファレンス | 0.2 | mA | ||

| 40kSPS モード | 0.5 | |||||

| 電流源 | プログラムによる | |||||

| IDVDD | デジタル電源電流 | 20SPS | 0.4 | 0.65 | mA | |

| 40kSPS | 0.6 | 0.85 | ||||

| パワーダウン・モード | 30 | 50 | μA | |||

| PD | 消費電力 | PGA モード | 20 | 32 | mW | |

| パワーダウン・モード | 0.1 | 0.2 | ||||

表 1 で強調表示されている「PGA バイパス」の部分は、PGA をバイパスした通常動作時に ADS1261 に引き込まれる平均アナログ電流が 2.7mA (標準値) または 4.5mA (最大値) であることを示しています。強調表示されている「機能別」の部分は、各機能をイネーブルにしたときの電流の増加量を示しています。これらの消費電流仕様はすべて、電流が安定した後にデバイスが引き込む平均電流を測定することで規定されています。

したがって、データシートの電源仕様では、デバイスまたはサポートしている回路が通常動作時に必要とするあらゆる過渡電流の要求を平均化しています。起動時およびスイッチング時の過渡電流が、データシートに規定されている値よりも大幅に大きくなる可能性があるため、これは重要です。信頼性の高いシステム設計を実現するには、平均電流と過渡電流の両方の需要に対応できる必要があります。

3 過渡電流

過渡電流に関する課題の 1 つは、ADC の動作条件や周囲の回路により、その大きさと持続時間が大幅に変化する可能性があることです。したがって、ADC のデータシートで過渡電流が規定されていることはほとんどありません。ただし、電源パターンと直列に配置した、抵抗値が小さい抵抗の両端をオシロスコープでプロービングし、特定のシステム構成で過渡電流を測定することは可能です。その後、オームの法則を使用して、結果として生じる電流を求めることができます。

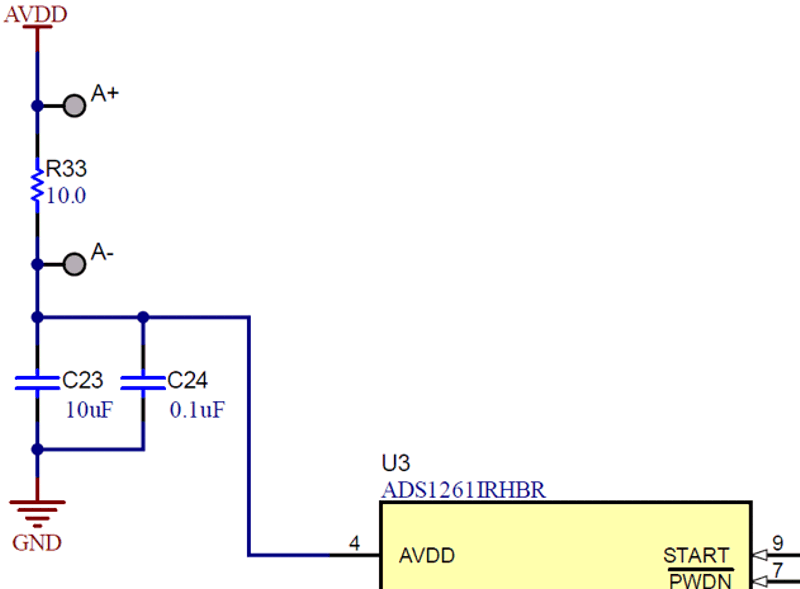

ADS1261 には、電源出力と ADC の AVDD ピンの間にこのような抵抗が組み込まれた、評価基板 (EVM) があります。10Ω の測定抵抗 (R33) を含む、EVM 回路図の関連部分を 図 1 に示します。この抵抗の両端での平均または過渡電圧降下を測定して 10Ω で除算すると、ADS1261 に引き込まれる平均または過渡電流がそれぞれ計算されます。この ADC の過渡電流の挙動をより的確に理解できるように、さまざまな条件下で複数のテストを実施しました。

図 1 ADS1261 EVM を使用した過渡電流テスト回路。

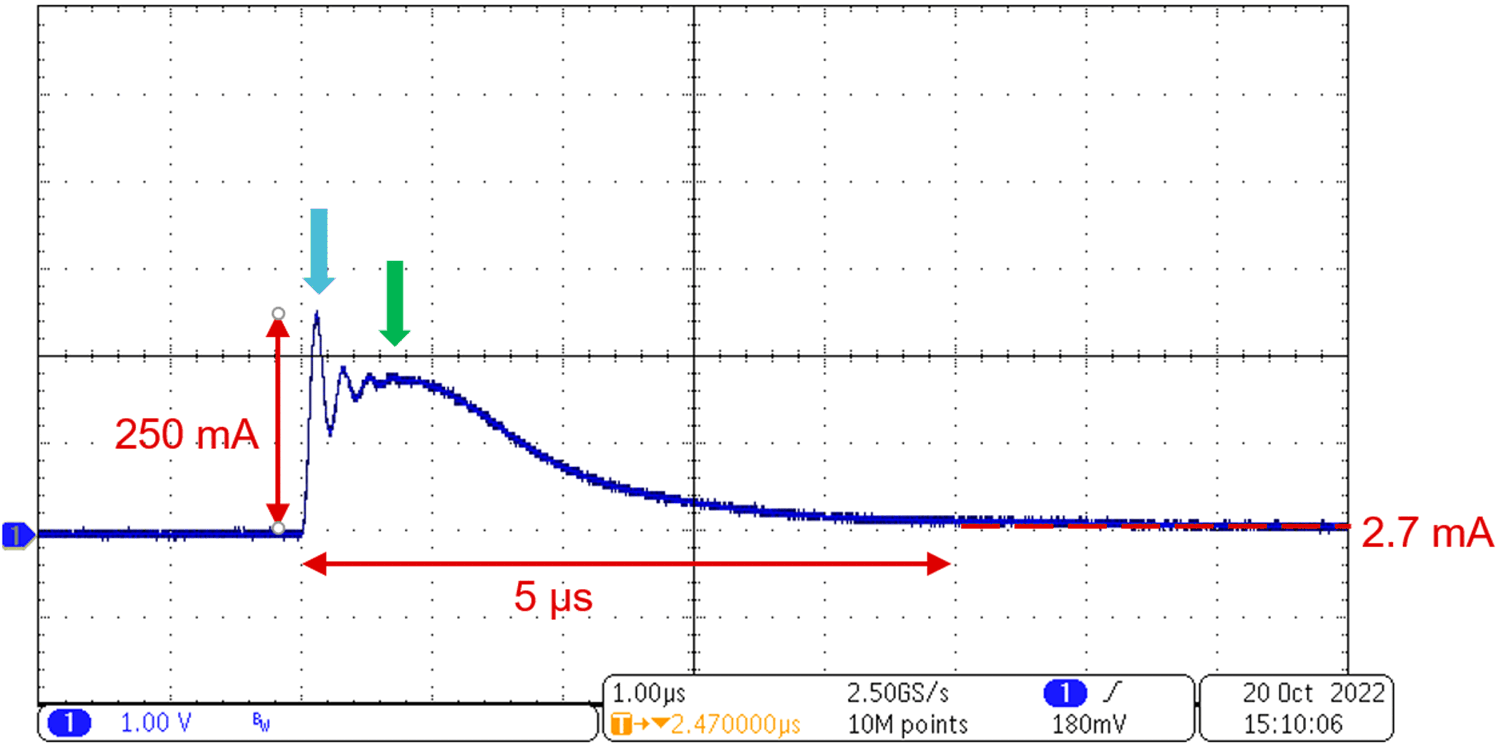

図 1 ADS1261 EVM を使用した過渡電流テスト回路。最初の過渡電流テストは、推奨される 10µF (C23) と 0.1µF (C24) のデカップリング コンデンサを AVDD とグランドとの間に取り付けたパワーアップ テストでした。図 2 に、これらの条件下での ADS1261 の過渡電流を示します。

図 2 デカップリング コンデンサを取り付けた状態で、パワーアップ時に測定された過渡電流。

図 2 デカップリング コンデンサを取り付けた状態で、パワーアップ時に測定された過渡電流。表 1 に示した ADS1261 の電源仕様によれば、PGA がディセーブルされた状態での平均電流は 2.7mA (標準値) または 4.5mA (最大値) となることに注意してください。ただし、図 2 の青い矢印は ADS1261 の最初の電源投入時に発生する 250mA の過渡スパイクを示しています。この過渡電流は、データシートに規定されている電流の標準値の 90 倍超、最大電流の 55 倍超です。ADC の状態が変化すると、同様の電流スパイクが発生する可能性があります。

図 2 の緑色の矢印は、デカップリング コンデンサの充電に必要な 2 番目の過渡電流を示しています。通常の動作条件では、デカップリング コンデンサに追加の電荷が蓄積され、過渡事象が発生したときに追加の電流を供給します。この追加の電荷は、ADC の動作に影響を及ぼさないように、安定した電源電圧を維持するのに役立ちます。ただし、これらのコンデンサは、システムに電力が供給されるときに、未充電状態から電源電圧まで充電する必要があります。電源が供給されていないコンデンサは、システム電源がオンになった瞬間は短絡のように動作し、大きな突入電流が発生します。デカップリング コンデンサの値が大きくなると、突入電流の大きさも大きくなります。

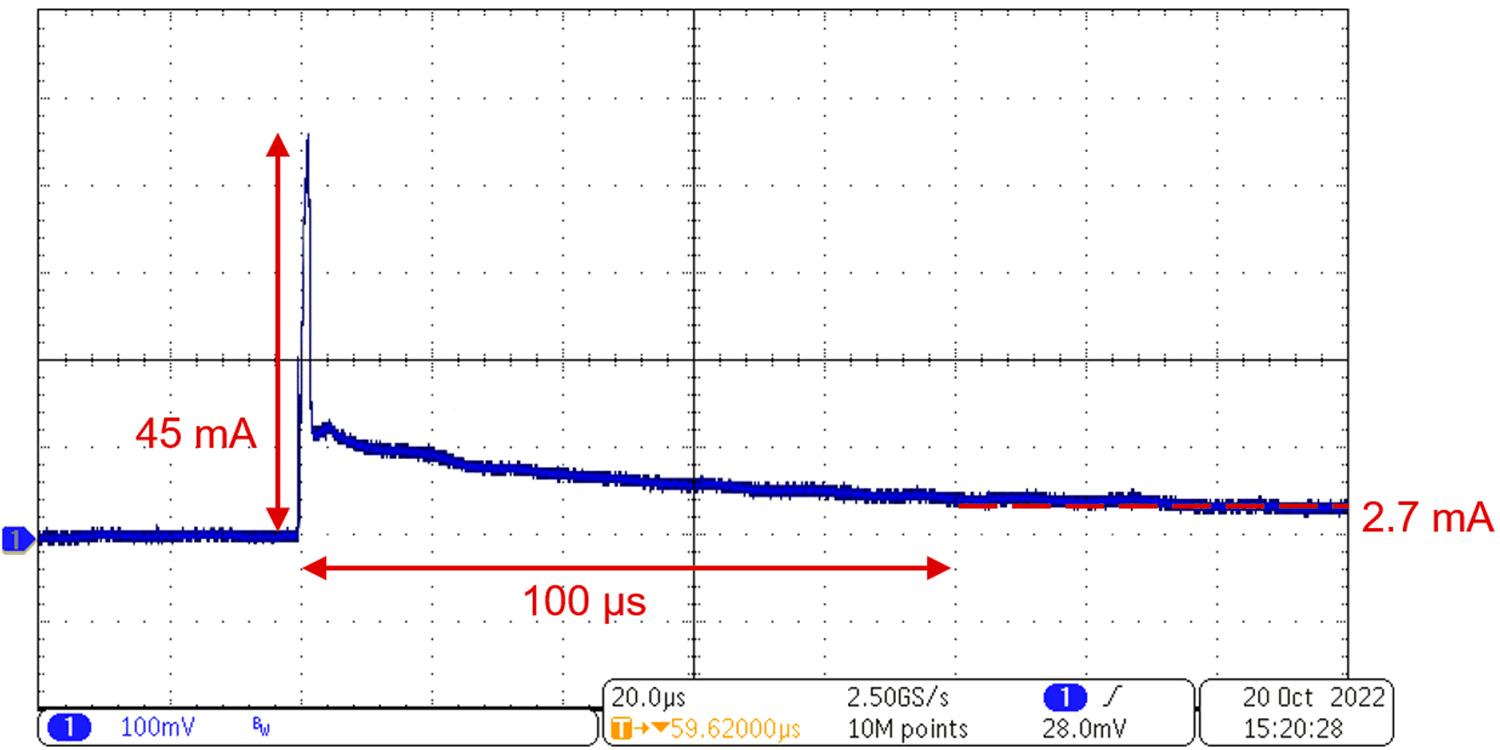

ADC に必要な過渡電流のみを測定するため、2 回目の過渡電流テストでは、図 1 でAVDD とグランドの間に挿入した推奨のデカップリング コンデンサ (10µF および 0.1µF) を取り外しました。図 3 に、これらの条件下での ADS1261 の過渡電流を示します。

図 3 デカップリング コンデンサを取り外した状態で、パワーアップ時に測定された過渡電流。

図 3 デカップリング コンデンサを取り外した状態で、パワーアップ時に測定された過渡電流。図 1 の 45mA の過渡スパイク電流は、スイッチングに起因する ADC に必要なパワーアップ電流のみを表しています。予想どおり、デカップリング コンデンサを取り付けたときに発生した 250mA のスパイクに比べて、ADC のみの過渡電流は小さくなっています。ただし、このように過渡振幅が小さくなると、ADC が定常状態の電流に達するまでの時間が大幅に長くなります。これは、コンデンサが補助電荷を供給しなくなるためです。また、この 45mA の過渡電流は、表 1 に示した 4.5mA の最大 ADC 電流仕様の 10 倍です。

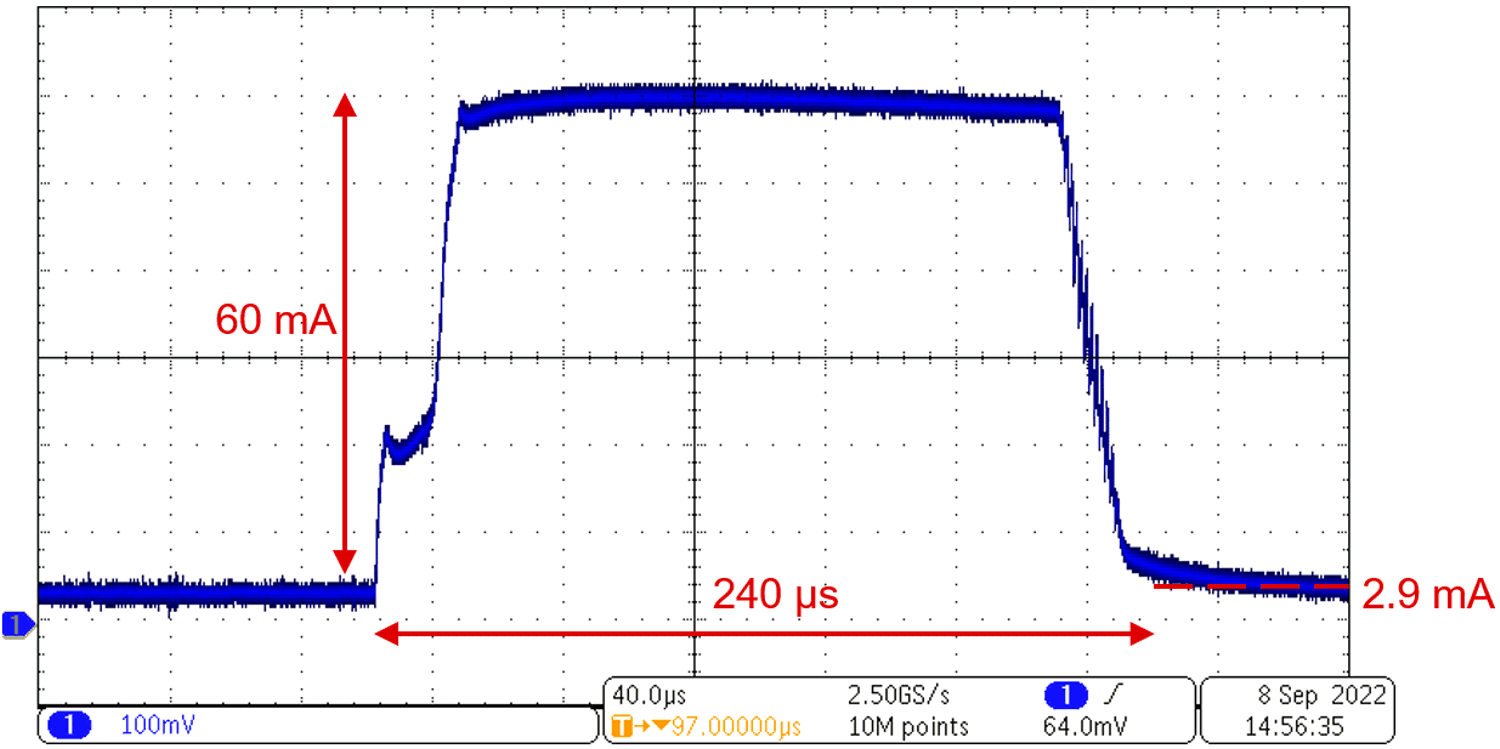

3 番目の一連のテストを実施し、さまざまな機能が過渡電流スパイクを引き起こす可能性があることも確認しました。ADS1261 の VREF をイネーブルにすることは、このようなスパイクを発生させる機能の 1 つでした。図 4 に、観測されたこの過渡電流の挙動を示します。

図 4 ADS1261 の VREF をイネーブルにした状態で測定された過渡電流。

図 4 ADS1261 の VREF をイネーブルにした状態で測定された過渡電流。表 1 から、ADS1261 の標準的な VREF 電流は 0.2 mA であることに注意してください。PGA をディセーブルにして (2.7mA) 内部 VREF がイネーブルの状態で ADC を動作させると、合計電流 2.9mA が生成されるはずです。ただし、図 4 で測定された 60mA の過渡電流は、予想した値の 20 倍を超えています。この過渡電流は、概ね VREF 出力ピンとグランドとの間に配置されたフィルタ コンデンサを充電するために必要な突入電流に起因します。

図 4 の興味深い特性の 1 つは、基本的に過渡パルス全体にわたって、電流需要が 60mA で一定に保たれることです。この挙動は ADS1261 の内部 VREF に設計された固有の電流制限のために発生し、REFOUT ピンがグランドに短絡した場合に ADC を保護するのに役立ちます。

すべての動作条件をテストしたわけではありませんが、追加の機能テストをいくつか実行したところ、測定可能な過渡電流は発生しませんでした。また、この動作は ADS1261 に限定されないことにも注意してください。この記事で説明した過渡電流は、すべての高精度 ADC で観測される可能性があります。