DLPU040C October 2016 – July 2024 DLP650LNIR , DLPC410

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

-

2Hardware

- 2.1

Key Components

- 2.1.1 Xilinx Virtex 5 APPSFPGA

- 2.1.2 DLPC410 - Digital Controller for DLP Discovery 4100 Chipset

- 2.1.3 DLPA200 - DMD Micromirror Driver

- 2.1.4 DLPR410 - Configuration PROM for DLPC410 Controller

- 2.1.5 APPSFPGA Flash Configuration PROM

- 2.1.6 DMD Connectors

- 2.1.7 USB Controller

- 2.1.8 50MHz Oscillator

- 2.1.9 DDR2 SODIMM Connector

- 2.1.10 Connectors

- 2.1.11 Battery

- 2.1.12 Power Supplies

- 2.2

Hardware Overview and Setup

- 2.2.1 Getting Started

- 2.2.2

User Connectors and I/O

- 2.2.2.1 J12 Input Power Connector

- 2.2.2.2 J18 Input Power Connector

- 2.2.2.3 J1 USB Connector Pinout

- 2.2.2.4 J3 USB GPIO

- 2.2.2.5 J6 GPIO_A Connector

- 2.2.2.6 J8 DLPC410 Mictor Connector

- 2.2.2.7 J9 USB/APPSFPGA Mictor Connector

- 2.2.2.8 J13 DMD Flex 1 Connector

- 2.2.2.9 J14 DMD Flex 2 Connector

- 2.2.2.10 J15 - DDR2 SODIMM Connector

- 2.2.2.11 J16, J17 EXP Connectors

- 2.2.2.12 H1 Xilinx FPGA JTAG Header

- 2.2.3 Configuration Jumpers

- 2.2.4 Switches

- 2.2.5 Power and Status LEDs

- 2.2.6 Test Points

- 2.1

Key Components

-

3Software

- 3.1 Overview

- 3.2 DLP Discovery 4100 Operation

- 3.3 Graphical User Interface

- 3.4 Script and Status Operations

- 3.5 DLPC410 Control Window

- 3.6 Test Patterns Window

- 3.7 About Box

- 3.8 Links

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation

- 7Revision History

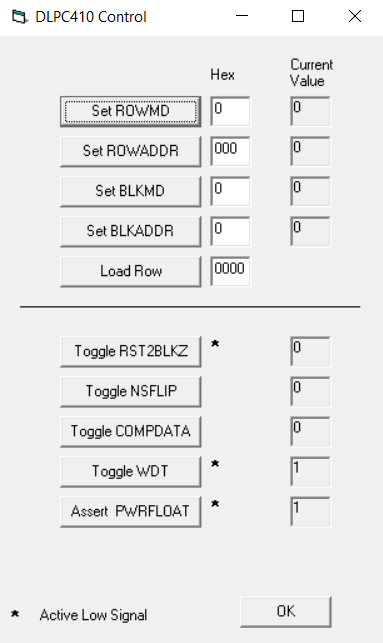

3.5 DLPC410 Control Window

The DLPC410 Control window is accessed through the DMD/DLPC410 Control menu and provides direct control of the DLPC410 input signals. No script commands are generated, the control is applied immediately to the DLPC410 when a Set button is clicked.

The upper portion of the window supports reading and setting of the DLPC410 signals used in writing data to the DMD. The current value for ROWMD (Row Mode), ROWADDR (Row Address), BLKMD (Block Mode), and BLKADDR (Block Address) is displayed in the Current Value column. When a new value is entered in Hexadecimal in the Hex column and the Set button is clicked the value sent to the DLPC410. The Load Row button sends one row with repeating values of the 4 digit hex value entered.

The lower portion of the window supports control of the DLPC410 input signals which are control operational modes. Click a button to toggle the current value of the signal.

Note: Asserting PWRFLOAT (Power Float) Parks the DMD mirrors. Recovery requires reset to the APPSFPGA either via asserting APPS_LOGIC_RST (HW switch SW2) or power cycling the EVM to restart the operation of the D4100 system again.

Refer to the DLPC410 data sheet (DLPS024) for detailed information on the DLPC410 input signals.

Refer to the DLP Discovery 4100 Development Platform API Programmer’s Guide (DLPU039) for detailed information about the ActiveX functions called by the buttons on this DMD/DLPC410 Control menu page.

Figure 3-29 DLPC410 Control Window

Figure 3-29 DLPC410 Control Window