DLPU040C October 2016 – July 2024 DLP650LNIR , DLPC410

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

-

2Hardware

- 2.1

Key Components

- 2.1.1 Xilinx Virtex 5 APPSFPGA

- 2.1.2 DLPC410 - Digital Controller for DLP Discovery 4100 Chipset

- 2.1.3 DLPA200 - DMD Micromirror Driver

- 2.1.4 DLPR410 - Configuration PROM for DLPC410 Controller

- 2.1.5 APPSFPGA Flash Configuration PROM

- 2.1.6 DMD Connectors

- 2.1.7 USB Controller

- 2.1.8 50MHz Oscillator

- 2.1.9 DDR2 SODIMM Connector

- 2.1.10 Connectors

- 2.1.11 Battery

- 2.1.12 Power Supplies

- 2.2

Hardware Overview and Setup

- 2.2.1 Getting Started

- 2.2.2

User Connectors and I/O

- 2.2.2.1 J12 Input Power Connector

- 2.2.2.2 J18 Input Power Connector

- 2.2.2.3 J1 USB Connector Pinout

- 2.2.2.4 J3 USB GPIO

- 2.2.2.5 J6 GPIO_A Connector

- 2.2.2.6 J8 DLPC410 Mictor Connector

- 2.2.2.7 J9 USB/APPSFPGA Mictor Connector

- 2.2.2.8 J13 DMD Flex 1 Connector

- 2.2.2.9 J14 DMD Flex 2 Connector

- 2.2.2.10 J15 - DDR2 SODIMM Connector

- 2.2.2.11 J16, J17 EXP Connectors

- 2.2.2.12 H1 Xilinx FPGA JTAG Header

- 2.2.3 Configuration Jumpers

- 2.2.4 Switches

- 2.2.5 Power and Status LEDs

- 2.2.6 Test Points

- 2.1

Key Components

-

3Software

- 3.1 Overview

- 3.2 DLP Discovery 4100 Operation

- 3.3 Graphical User Interface

- 3.4 Script and Status Operations

- 3.5 DLPC410 Control Window

- 3.6 Test Patterns Window

- 3.7 About Box

- 3.8 Links

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation

- 7Revision History

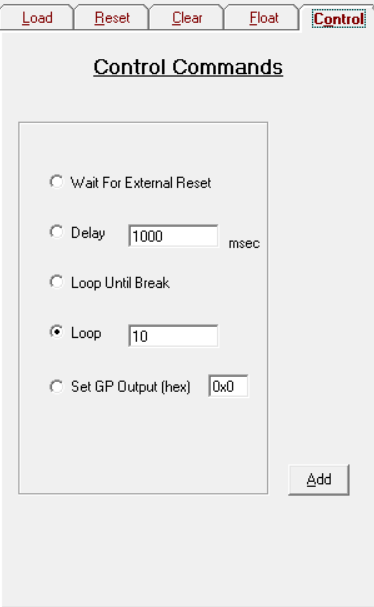

3.3.3.5 Control Tab

The Control commands tab supports commands for script execution control, external reset, and digital output:

- The Wait for External Reset scripting command waits 10 seconds for an external global reset triggered by a rising edge on APPSFPGA input GPIO_A0. After 10 seconds, execution of the script resumes with the next command in the script. GPIO_A0 is a 2.5 Volt CMOS input.

- The Delay command delays for the specified time in msec.

- The Loop Until Break command loops until the Break button is clicked.

- The Loop command loops for the specified number of iterations.

- The Set GP Output command sets the value of the APPSFPGA general purpose digital

outputs GPIO_A(4 - 6). Value is entered in decimal or hexadecimal (for example, 0x3). Bits

0, 1, 2 of value control the output state of GPIO_A4, GPIO_A5, and GPIO_A6 respectively.

Bits 7, 6, 5, 4, 3 of Value are not used. GPIO_A(4 - 6) are 2.5 Volt CMOS outputs.

Note: NOTE: For more information on GPIO outputs see the DLP® Discovery™ 4100 Development Platform API Programmer’s Guide (DLPU039 § 5.2.24 and § 6.2.24).

Figure 3-26 Control Tab

Figure 3-26 Control Tab