DLPU132A October 2023 – March 2024 DLPC964

- 1

- Description

- Get Started

- Features

- Applications

- 6

- 1Evaluation Module Overview

-

2Hardware

- 2.1 DLPLCRC964EVM Power Supply Requirements

- 2.2

DLPLCRC964EVM Connections

- 2.2.1 J1, J2 - HPC FMC Connector (Male)

- 2.2.2 J3 - Input Power

- 2.2.3 J4 - TestMux Connector

- 2.2.4 J6, J8 - I2C Address Selectors

- 2.2.5 J7 - JTAG Boundary Scan

- 2.2.6 J9 - Micro-B USB Connector

- 2.2.7 J10 - I2C Connector

- 2.2.8 J11 - 3.3V GPIO Connector

- 2.2.9 J12 - 1.8V GPIO Connector

- 2.2.10 J13, J14, J15, J16 - DMD EVM Board Flex Cable Connectors

- 2.2.11 J17 - DMD_DMux Connector

- 2.2.12 J18 - FanSink Connector

- 2.2.13 Switches

- 2.2.14 DLP LightCrafter DLPC964 LEDs

- 2.3 EVM Assembly

- 2.4 Quick Start

- 3Software

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation from Texas Instruments

- 7Revision History

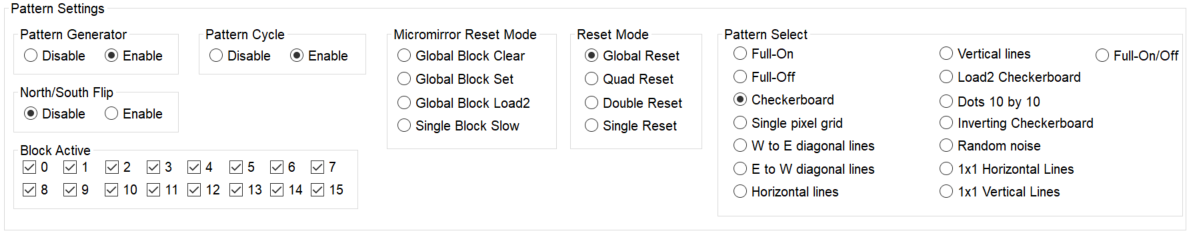

3.1.4.4.5 Pattern Settings (Apps)

Figure 3-17 Apps FPGA Pattern

Settings

Figure 3-17 Apps FPGA Pattern

Settings- Pattern Generator - When enabled, patterns are displayed onto the DMD. When disabled, no patterns are going to be displayed on DMD.

- Pattern Cycle - When enabled, the DMD cycles through the first 8 predefined patterns, each being displayed every 2 seconds. When disabled, a single selected pattern is sent to the DMD.

- North/South Flip - Having this enabled flips the image being displayed on the DMD vertically.

- Pattern Select

- Full-On - Full white background where all mirrors on the DMD are going to be in the on position.

- Full-Off - Full black background where all mirrors on the DMD are going to be in the off position.

- Checkerboard - Black and white checkerboard (64 x 64 pixels).

- Single pixel grid - The border is on to help visualize the extent of the DMD array.

- W to E diagonal lines - Used to check for row data issues.

- E to W diagonal lines - Used to check for row data issues.

- Horizontal lines - Used to check for issues with row loads.

- Vertical lines - Used to check for issues with data bus lines.

- Load2 Checkboard - A black and white checkerboard pattern (32 x 32 pixels).

- Dots 10 by 10 - Single white pixels are spaced 10 pixels evenly in the X and Y direction.

- Inverting Checkerboard - Inverted version of the checkerboard pattern.

- Random Noise - Randomized noise pattern for customer tilt angle testing.

- 1x1 Horizontal lines (every row alternating black/white) - Used to check for issues with row loads.

- 1x1 Vertical lines (every column alternating black/white) - Used to check for issues with data bus lines.

- Full-On/Off - Toggles between the Full-On and Full-Off pattern.

- Micromirror Reset Mode

- Global Block Clear - This mode shows how the Clear block load type is used in the DLPC964 system. A clear load type does not require any data since the block puts all of the mirrors in the off state (0). Since the clear load type does not have any data to be sent, the command valid signal is not needed so only the DMD load signal is sent. The MCP_Start signal follows the same pattern as Global Mode.

- Global Block Set - This mode shows how the Set block load type is used in the DLPC964 system. A set load type does the opposite of the clear load type and also does not require any data. The set load type sets all the mirrors in the on state (1). Just like the clear load type, there is no need for the command valid signal, only the DMD load signal. The MCP_Start signal follows the same pattern as Global Mode.

- Global Block Load2 - Enabling the Load2 operation tells the DMD to load 1 line of data received into 2 rows of the DMD. The role of the DLPC964 Apps FPGA during a Load2 operation is to verify that 68 lines, at most, are sent over the Aurora HSSI channels. Asserting LOAD2 causes the DLPC964 controller and attached DMD to load 2 rows for every row of data sent, reducing the pattern load time to half of a full DMD load. This function does not reduce the MCP timing.

- Single Block Slow - Slow mode (or disabling the fast mode) causes the DLPC964 Apps FPGA to send data across a single Aurora 64B/66B channel only (4x 10Gbps lanes compared to 12x). To do this, each segment of a block must be sent sequentially across 1 channel instead of parallel. The segments must be sent in the following order: D (0x3) C (0x2) B (0x1) A (0x0). Once all four segments are sent, the MCP_Start signal can be issued. The MCP_Start signal behaves the same as in Single Mode.

- Block Active - There are 16 blocks [0-15] in the DLP991U DMD. The blocks that are checked inside the GUI are going to determine what blocks are going to be reset and loaded with new data to the DMD.