DLPU132A October 2023 – March 2024 DLPC964

- 1

- Description

- Get Started

- Features

- Applications

- 6

- 1Evaluation Module Overview

-

2Hardware

- 2.1 DLPLCRC964EVM Power Supply Requirements

- 2.2

DLPLCRC964EVM Connections

- 2.2.1 J1, J2 - HPC FMC Connector (Male)

- 2.2.2 J3 - Input Power

- 2.2.3 J4 - TestMux Connector

- 2.2.4 J6, J8 - I2C Address Selectors

- 2.2.5 J7 - JTAG Boundary Scan

- 2.2.6 J9 - Micro-B USB Connector

- 2.2.7 J10 - I2C Connector

- 2.2.8 J11 - 3.3V GPIO Connector

- 2.2.9 J12 - 1.8V GPIO Connector

- 2.2.10 J13, J14, J15, J16 - DMD EVM Board Flex Cable Connectors

- 2.2.11 J17 - DMD_DMux Connector

- 2.2.12 J18 - FanSink Connector

- 2.2.13 Switches

- 2.2.14 DLP LightCrafter DLPC964 LEDs

- 2.3 EVM Assembly

- 2.4 Quick Start

- 3Software

- 4Hardware Design Files

- 5Additional Information

- 6Related Documentation from Texas Instruments

- 7Revision History

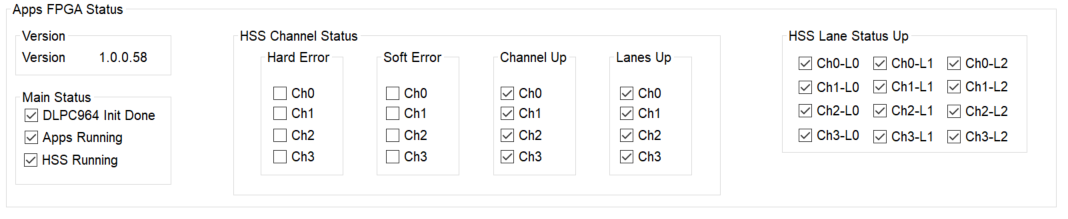

3.1.4.4.1 Apps FPGA Status

Figure 3-13 Apps FPGA Status

Figure 3-13 Apps FPGA Status- Apps FPGA Version - Contains the build number and version information for the Apps FPGA Firmware.

- Main Status - This contains the status for the DLPC964, Apps FPGA, and HSS status determining if each one is up and running.

- HSS Channel Status - HSS

Channel Status indicates the status of the Aurora 64B/66B inputs to the DLPC964

Controller.

- Hard Error - Input Aurora Channel 0-3 hard error and indicates failure in the GTH.

- Soft Error - The HSS Soft Error Count indicates corrupted data received on each individual channel.

- Channel Up - Determines if the HSS Aurora Channels 0-3 are initialized.

- Lanes Up - Determines if the HSS Aurora Lane Channels 0-3 are initialized.

- HSS Lane Status Up - The HSS Lane Status Up indicates the status of each individual lane of the Aurora 64B/66B input to the DLPC964 Controller.