GERA028A June 2021 – September 2022 AMC3301 , AMC3301-Q1 , AMC3302 , AMC3302-Q1 , AMC3306M05 , AMC3306M25 , AMC3330 , AMC3330-Q1 , AMC3336 , AMC3336-Q1

4.2 Bewährte Methoden für das Leiterplatten-Layout für mehrere AMC3301

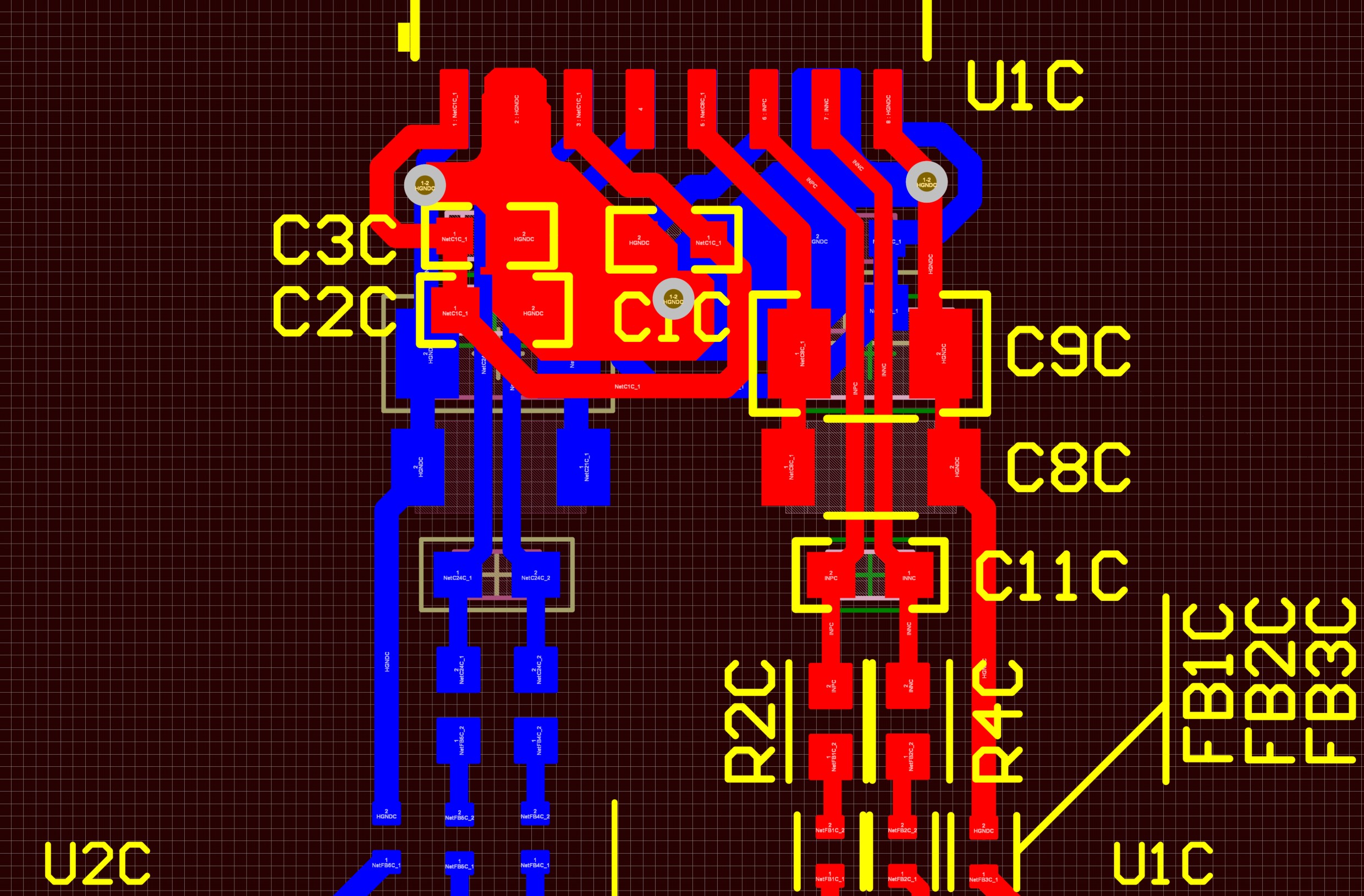

Der bei der Prüfung verwendete Schaltplan ist der gleiche wie der Ferrit-Abschnitt von Abbildung 4-3. Das Layout zum Stapeln der AMC3301 ist jedoch in Abbildung 4-3 dargestellt.

Abbildung 4-3 Empfohlenes Layout für mehrere AMC3301-Bausteine

Abbildung 4-3 Empfohlenes Layout für mehrere AMC3301-BausteineIm Allgemeinen werden die gleichen in Sektion 3.2 beschriebenen Layoutprinzipien mit einem zweilagigen Leiterplattendesign befolgt.

Allerdings wird ein direkter und induktivitätsarmer Pfad von Pin 2 (DCDC_HGND) zu Pin 8 (HGND) jedes Bausteins unterschiedlich erreicht. Anstelle einer Spur verbindet eine Sternverbindung beide Bausteine zwischen der oberen und der unteren Schicht an den Pins 4 und 5. Darüber hinaus wird ein Kupferpool verwendet, um die DC/DC-Kondensatoren mit DCDC_HGND auf derselben Schicht zu verbinden.

Schließlich werden die LDO_OUT-Kondensatoren auf ein 1206-Gehäuse skaliert, um einen direkten und unterbrechungsfreien Pfad für die positiven und negativen Eingänge unter den Kondensatoren zu ermöglichen.