KOKA017A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

1 MSPM0L 하드웨어 설계 검사 목록

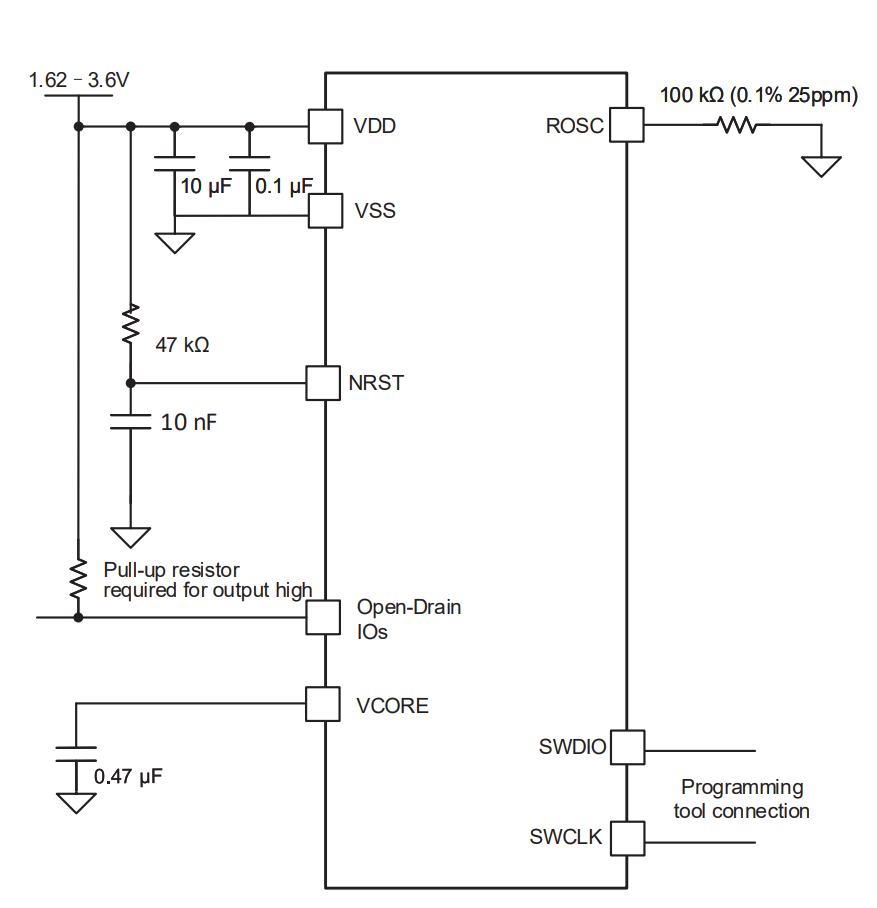

표 1-1에서는 MSPM0L 하드웨어 설계 과정에서 확인해야 할 주요 신호에 대해 설명합니다. 다음 섹션에 자세한 내용이 나와 있습니다.

| 핀 (1) | 설명 | 요구 사항 |

|---|---|---|

| VDD | 전원 공급 장치 양극 핀 | VDD와 VSS 사이에 10µF 및 100nF 커패시터를 배치하고 해당 부품을 VDD 및 VSS에 가깝게 유지합니다. |

| VSS | 전원 공급 장치 음극 핀 | |

| VCORE | 코어 전압(일반: 1.35V) | 470nF 커패시터를 VSS에 연결하고, 전압을 공급하거나 VCORE 핀에 외부 부하를 가하지 않습니다. |

| NRST | 리셋 핀 | 외부 47kΩ 풀업 저항을 10nF 풀다운 커패시터와 연결합니다. |

| ROSC | 외부 레퍼런스 저항 핀 |

|

| VREF+ | 외부 레퍼런스 입력을 위한 전압 레퍼런스 전원 공급 장치 |

|

| VREF- | 외부 레퍼런스 입력을 위한 전압 레퍼런스 접지 공급 장치 | |

| SWCLK | 디버그 프로브의 직렬 와이어 클록 | VDD로의 내부 풀업, 외부 부품이 필요하지 않습니다. |

| SWDIO | 양방향(공유) 직렬 와이어 데이터 | VSS로의 내부 풀다운, 외부 부품이 필요하지 않습니다. |

| PA0, PA1 | 오픈 드레인 I/O | 높은 출력에 필요한 풀업 저항 |

| PA18 | 기본 BSL 호출 핀 | 리셋 후 BSL 모드로 전환되지 않도록 계속 풀다운하십시오. BSL 호출 핀을 다시 매핑할 수 있습니다. |

| PAx(PA0, PA1 제외) | 범용 I/O | 해당 핀 기능을 GPIO(PINCMx.PF = 0x1)로 설정하고 사용하지 않는 핀을 내부 풀업 또는 풀다운 저항을 사용하여 낮은 출력 또는 입력으로 구성합니다. |

| OPAx_IN0-(2) | OPAx 인버팅 단자 입력 0 | 이 핀은 임피던스가 높으며 사용하지 않는 경우 외부 부품이 필요하지 않습니다. |

TI는 10μF 및 0.1nF의 낮은 ESR 세라믹 디커플링 커패시터 조합을 VDD 및 VSS 핀에 연결할 것을 권장합니다. 더 높은 값의 커패시터를 사용할 수 있지만 공급 레일 램프업 시간에 영향을 줄 수 있습니다. 디커플링 커패시터는 분리되는 핀에 최대한 가깝게 배치해야 합니다(몇 밀리미터 이내).

NRST 리셋 핀은 외부 47kΩ 풀업 저항을 10nF 풀다운 커패시터와 연결하는 데 필요합니다.

SYSOSC 주파수 보정 루프(FCL) 회로는 ROSC 핀과 VSS 사이에 채워진 외부 100kΩ 저항을 사용하여 SYSOSC에 대한 정밀한 레퍼런스 전류를 제공함으로써 SYSOSC 주파수를 안정화합니다. SYSOSC FCL이 활성화되지 않은 경우 이 저항이 필요하지 않습니다.

VCORE 핀에는 0.47µF 탱크 커패시터가 필요하며 장치 접지까지의 최소 거리를 가진 장치 가까이에 배치해야 합니다.

5V 허용 오픈 드레인(ODIO)의 경우 높은 출력을 위해서는 풀업 저항이 필요하며, ODIO를 사용할 경우 I2C 및 UART 기능에 필요합니다.

그림 1-1 MSPM0L 일반 애플리케이션 회로도

그림 1-1 MSPM0L 일반 애플리케이션 회로도