KOKA017A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

9.4 보드 레이어 및 권장 스택업을 선택하는 방법

고속 신호의 반사를 줄이려면 소스, 싱크 및 전송 라인 간의 임피던스를 일치시켜야 합니다. 신호 트레이스의 임피던스는 지오메트리 및 레퍼런스 플레인에 대한 위치에 따라 달라집니다.

특정 임피던스 요구 사항에 대한 차동 쌍 사이의 트레이스 폭과 공간은 선택한 PCB 스택업에 따라 달라집니다. PCB 기술의 유형과 비용 요구 사항에 따라 최소 트레이스 폭과 공간에 제한이 있으므로 필요한 모든 임피던스를 실현할 수 있는 PCB 스택업을 선택해야 합니다.

사용할 수 있는 최소 구성은 2 스택업입니다. 여러 개의 고속 신호를 가진 매우 밀도가 높은 PCB에는 4레이어 또는 6레이어 보드가 필요합니다.

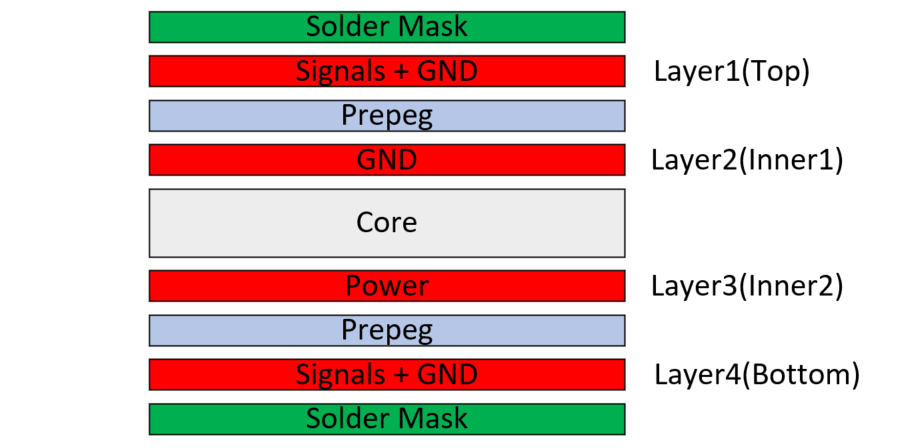

다음 스택업(그림 9-5 참조)은 스택업 평가 및 선택에 도움이 되는 시작점으로 사용할 수 있는 4계층 예시입니다. 이러한 스택업 구성은 전력 플레인에 인접한 GND 플레인을 사용하여 커패시턴스를 높이고 GND와 전력 플레인 사이의 간격을 줄입니다. 따라서 최상위 레이어의 고속 신호는 레이어 수가 증가하고 각 PCB 신호 레이어에 대해 GND 레퍼런스가 있으면 방사 EMC 성능이 더욱 향상되므로 EMC 방출을 줄이는 데 도움이 되는 견고한 GND 레퍼런스 플레인을 갖게 됩니다.

그림 9-5 4레이어 PCB 스택업의 예

그림 9-5 4레이어 PCB 스택업의 예시스템이 그다지 복잡하지 않고 고속 신호 또는 민감한 아날로그 신호가 없으면 2 스택업 구조로 충분합니다.