KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.2 접지 배치를 위한 고려 사항

시스템 접지는 보드의 잡음 및 EMI 문제와 관련된 가장 중요한 영역이자 기초입니다. 이러한 문제를 최소화하는 가장 실용적인 방법은 별도의 접지면을 사용하는 것입니다.

접지 잡음이란?

회로(예: 드라이버)에서 발생하는 각 신호에는 접지 경로를 통해 리턴되는 전류 흐름이 있습니다. 주파수가 증가함에 따라 또는 릴레이와 같이 단순한 고전류 스위칭의 경우에도 접지 방식에서 간섭을 생성하는 라인 임피던스로 인해 전압 강하가 발생합니다. 리턴 경로는 항상 최소 저항을 통해 이루어집니다. DC 신호의 경우 가장 낮은 저항 경로가 되고,고주파 신호의 경우 가장 낮은 임피던스 경로가 됩니다. 이는 접지면이 문제를 단순화하는 방법을 설명하고 신호 무결성을 보장하는 열쇠입니다.

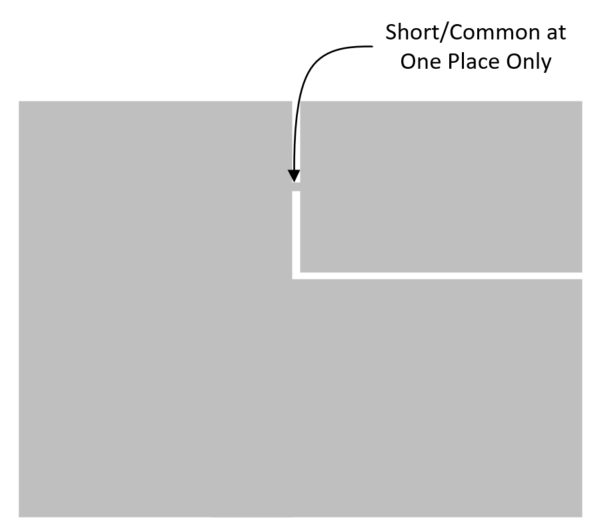

디지털 리턴 신호는 아날로그 리턴(접지) 영역 내부로 전파되지 않는 것이 좋습니다. 따라서 설계자는 반드시 접지면을 분할하여 모든 디지털 신호 리턴 루프를 접지 영역 내에 두도록 해야 합니다. 이 분할은 신중하게 수행해야 합니다. 많은 설계에서 단일(공통) 전압 레귤레이터를 사용하여 동일한 전압 레벨(예: 3.3V)의 디지털 및 아날로그 전원 공급 장치를 생성합니다. 아날로그 레일과 디지털 전원 공급 레일 및 각각의 접지를 서로 절연해야 합니다. 접지를 절연할 때는 두 접지 모두 어딘가에서 단락되어야 하는 점에 주의하십시오. 그림 9-2에서는 디지털 신호의 가능한 리턴 경로가 아날로그 접지를 통과하는 루프를 형성하지 못하도록 하는 방법을 보여줍니다. 각 설계에서 구성 요소 배치 등을 고려하여 공통점을 결정합니다. 접지 트레이스가 있는 직렬에 인덕터(페라이트 비드) 또는 저항(제로 Ω도 아님)을 추가하지 마십시오. 고주파수에서의 관련 인덕턴스로 인해 임피던스가 증가하여 전압 차동을 유발합니다. 디지털 접지로 참조되는 신호를 아날로그 접지 또는 다른 방향으로 라우팅하지 마십시오.

그림 9-2 디지털 및 아날로그 접지 및 공통 영역

그림 9-2 디지털 및 아날로그 접지 및 공통 영역