KOKA018B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

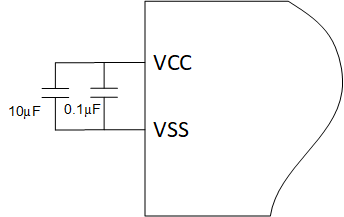

2.4 전원 공급 장치에 권장되는 디커플링 회로

TI는 10μF + 100nF 저 ESR 세라믹 디커플링 커패시터 조합을 DVCC 핀에 연결하는 것을 권장합니다(그림 2-3 참조). 더 높은 값의 커패시터를 사용할 수 있지만 공급 레일 램프업 시간에 영향을 줄 수 있습니다. 디커플링 커패시터는 분리되는 핀에 최대한 가깝게 배치해야 합니다(몇 밀리미터 이내).

그림 2-3 전원 공급 장치 디커플링 회로

그림 2-3 전원 공급 장치 디커플링 회로