KOKA069A January 2019 – June 2024 AMC1311 , AMC1411 , ISO224

설계 목표

| 전압 소스 | ISO224 입력 전압 | ISO224 출력 전압 VDD2/2 공통 모드(VOUTP – VOUTN) | 전원 공급 장치 | ||||

|---|---|---|---|---|---|---|---|

| VMAX | VMIN | VIN, MAX | VIN, MIN | VOUT, MAX | VOUT, MIN | VDD1 | VDD2 |

| 480V | -480V | 12V | -12V | 4V | -4V | 4.5V~18V | 4.5V~5.5V |

설계 설명

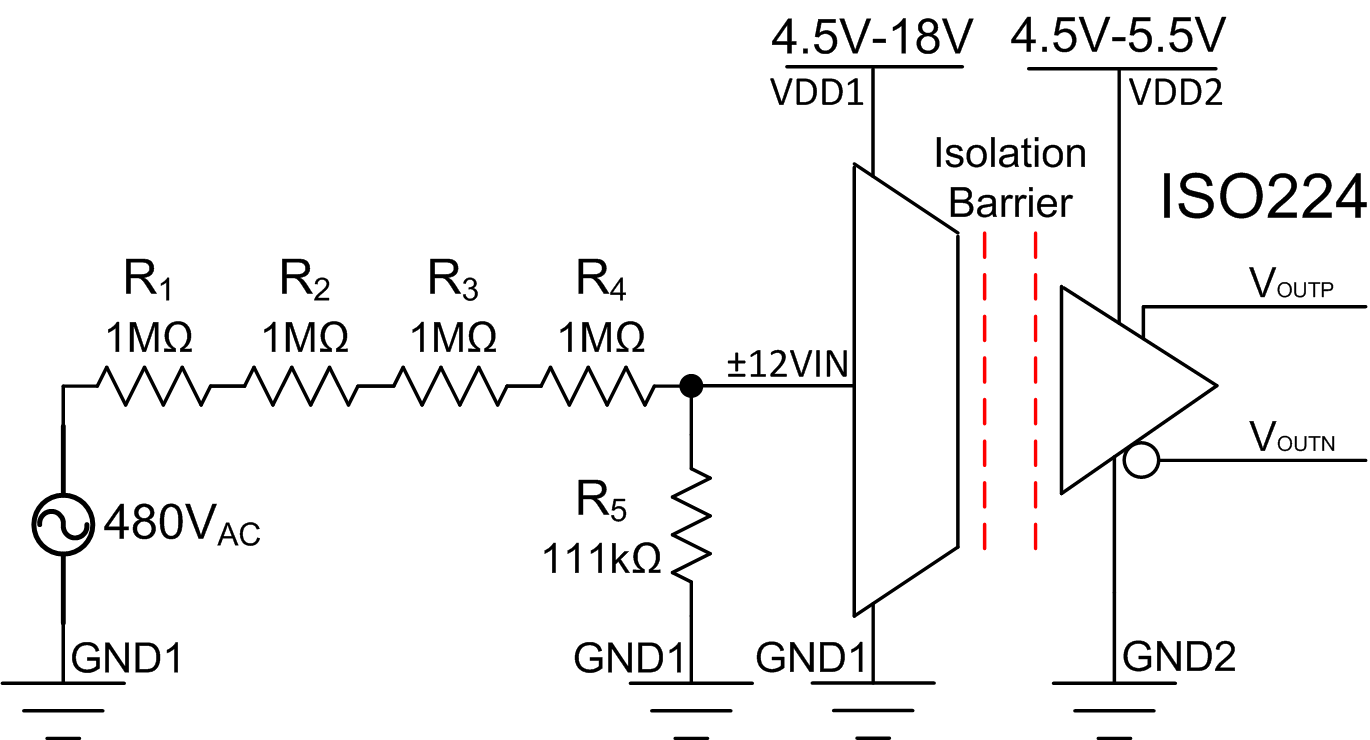

이 회로는 ISO224 절연 증폭기와 전압 분할기 회로를 활용하여 ±480V, 절연, 전압 감지 측정을 수행합니다. 전압 분할기 회로는 전압을 ±480V에서 ±12V로 줄여 ISO224의 입력 범위에 일치시킵니다. ISO224는 고압측 및 저압측 전원 공급 장치로부터 전원을 공급받습니다. 일반적으로 고압측 공급은 부동 공급을 사용하거나 절연 변압기 또는 절연 DC/DC 컨버터를 사용하여 저압측에서 생성됩니다. ISO224는 ⅓V/V의 고정 게인으로 ±12V 단일 종단 신호를 측정하고 출력 공통 모드 전압이 VDD2 / 2인 ±4V의 절연 차동 출력 전압을 출력할 수 있습니다. SBOA274에 나와 있는 것처럼 TLV6001과 같은 추가 연산 증폭기를 사용하여 필요에 따라 차동 출력 전압을 확장할 수 있습니다.

설계 노트

- 원하는 입력 신호 범위에 대한 시스템의 선형 작동을 확인하십시오. 이는 DC 전송 특성 섹션의 시뮬레이션을 사용하여 검증됩니다.

- 저항 분할기 회로(R1–R5)에 사용되는 저항이 전압 소스에서 공급되는 전원을 소산할 수 있는지 확인하십시오.

- 데이터 시트의 절대 최대 정격 값 표에 설명된 대로 ISO224 입력의 전압이 ±15V 미만인지 확인하고 입력 값에 ±10mA 미만이 적용되었는지 확인하십시오. 시스템이 과도 현상에 취약할 경우 입력에 TVS 다이오드를 추가하는 것을 고려해 보십시오. 자세한 내용은 ±12V의 단일 종단 입력과 ±4V 데이터의 차동 출력을 지원하는 ISO224 강화 절연 증폭기의 입력 클램프 보호 회로의 I-V 곡선 이미지를 참조하십시오.

설계 단계

- 전압 소스부터 전압 분할기 회로에 대한 ISO224의 입력 전압의 비율을 계산합니다.

- ISO224의 일반적인 입력 임피던스는 1.25MΩ입니다. 이 임피던스는 저항 R5와 병렬로 연결되어 있으므로, 전압 분할기 회로를 설계할 때 반드시 고려해야 합니다. R1, R2, R3 및 R4에 대해 1MΩ 저항을 선택합니다. 이전 단계와 다음 전압 분할기 방정식의 비율을 사용하여 R5의 전압 분할기 병렬 조합( || )과 ISO224 입력 임피던스에 필요한 등가 저항을 계산합니다.

- ISO224 입력 임피던스의 1.25MΩ을 대입하고 다음 방정식을 사용하여 R5를 대입합니다. 아날로그 엔지니어의 계산기를 사용하여 R5에 가장 근접한 표준 값을 결정합니다.

- 등가 저항이 2단계에서 계산된 저항과 가까운지 확인합니다.

- 전압 분할기 회로가 합리적인 오차 범위 내에 있는지 확인합니다. 다음 계산의 경우 ISO224의 입력 저항은 일반 값 1.25MΩ으로 가정되며, 그 결과 오류는 0.6%입니다. 그러나 내부 클램프 보호 회로의 저항 변화에 따라 입력 저항이 장치마다 다르다는 것을 고려하는 것이 중요합니다. 최소 입력 저항 1MΩ을 사용하여 동일한 계산을 수행하면 오류가 2.5%입니다. 이 오류 범위가 허용되지 않는 경우 보정을 수행하거나 전압 분할기 회로의 저항을 줄일 수 있습니다.

- 전력 손실이 저항의 정격을 초과하지 않도록 전압 소스에서 전압 분할기 회로를 통해 흐르는 전류를 계산합니다. 자세한 내용은 고전압 측정의 고려 사항을 참조하십시오.

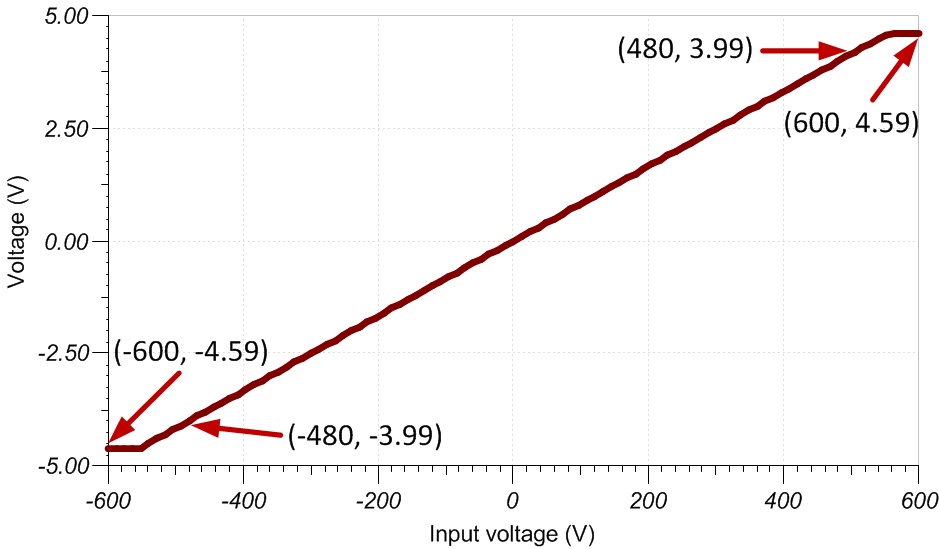

DC 전송 특성

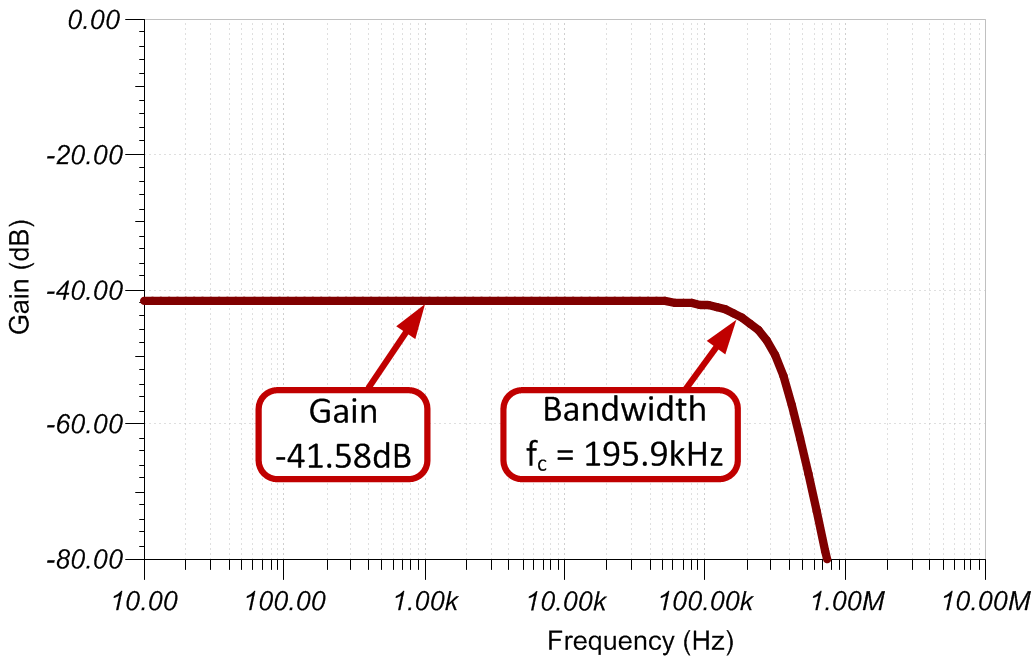

다음 그래프는 ±600V 입력의 시뮬레이션된 출력을 보여줍니다. 전압 분할기는 게인을 1/40까지 확장하며, ISO224는 게인을 추가 ⅓로 확장합니다.

전송 기능은 전압 분할기에서 1/40을 나타내고 ISO224에서 ⅓을 나타냅니다(즉, 게인 × VIN = VOUT, (1/40) × (⅓) × (480V) = 4V).

참고 자료

- 아날로그 엔지니어의 회로 안내서

- SPICE시뮬레이션 파일 SBAC232

- TI 정밀 설계 TIDA-00835

- TI Precision Labs

주요 절연 연산 증폭기 설계

| ISO224B | |

|---|---|

| VDD1 | 4.5V~18V |

| VDD2 | 4.5V~5.5V |

| 입력 전압 범위 | ±12V |

| 공칭 게인 | ⅓ |

| VOUT | VDD2/2의 출력 공통 모드에서 차동 ±4V |

| 입력 저항 | 1.25MΩ(일반) |

| 작은 신호 대역폭 | 275kHz |

| 입력 오프셋 전압 및 드리프트 | ±5mV(최대), ±15µV/°C(최대) |

| 게인 오류 및 드리프트 | ±0.3%(최대), ±35ppm/°C(최대) |

| 비선형성 및 드리프트 | 0.01%(최대), ±0.1ppm/°C(일반) |

| 절연 과도 과전압 | 7kVPEAK |

| 작동 전압 | 1.5kVRMS |

| CMTI(공통 모드 과도 내성) | 55 kV/µs(최소) |

| ISO224 | |

대체 절연 연산 증폭기 설계

| AMC1311B | |

|---|---|

| VDD1 | 3V~5.5V |

| VDD2 | 3V~5.5V |

| 입력 전압 범위 | 2V |

| 공칭 게인 | 1 |

| VOUT | 1.44V의 출력 공통 모드에서 차동 ±2V |

| 입력 저항 | 1GΩ(일반) |

| 작은 신호 대역폭 | 220kHz |

| 입력 오프셋 전압 및 드리프트 | ±1.5mV(최대), ±15µV/°C(최대) |

| 게인 오류 및 드리프트 | ±0.3%(최대), ±45ppm/°C(최대) |

| 비선형성 및 드리프트 | 0.01%, 1ppm/°C(일반) |

| 절연 과도 과전압 | 7kVPEAK |

| 작동 전압 | 1.5kVRMS |

| CMTI(공통 모드 과도 내성) | 75kV/µs(최소) |

| AMC1311 | |