NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1227-Q1 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2227-Q1 , MSPM0L2228 , MSPM0L2228-Q1

6.1 ADC 設計考量

MSPM0L 裝置具有 12 位元、高達 1-Msps 的類比轉數位轉換器 (ADC)。ADC 支援快速的 12 位元、10 位元和 8 位元類比轉數位轉換。ADC 執行 12 位元 SAR 核心、取樣/轉換模式控制,以及多達 4 個獨立轉換與控制緩衝器。

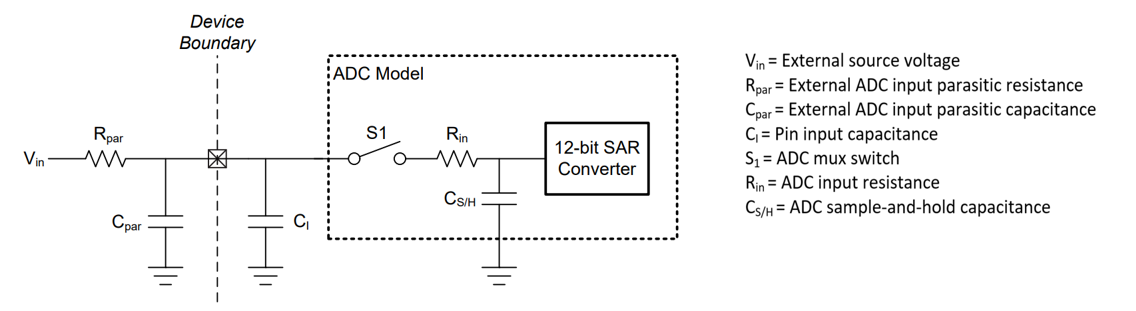

圖 6-1 ADC 輸入網路

圖 6-1 ADC 輸入網路若要達到所需的轉換速度並維持高準確度,請在硬體設計中設定適當取樣時間。取樣 (取樣保持) 時間決定在數位轉換前多久時間進行訊號取樣。在取樣期間,內部開關會讓輸入電容器充電。將電容器完全充電的所需時間,視連接至 ADC 輸入接腳的外部類比前端 (AFE) 而定。圖 6-1顯示 MSPM0L MCU 的典型 ADC 模型。Rin 和 CS/H 值可從特定裝置的產品規格書中取得。了解 AFE 驅動器功能並計算訊號取樣所需的最短取樣時間非常重要。RPar 和 Rin 的電阻會影響 tsample。方程式 1可用於計算 n 位元轉換的最短取樣時間 tsample 的保守值:

方程式 1. tsample ≥ (Rpar + Rin) × ln(2n+2) × (CS/H + C1 + CPar)