NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

10.2.2 硬體叫用

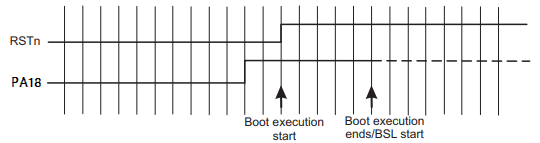

開機載入程式支援透過使用 GPIO 執行 BOOTRST 後叫用硬體。NONMAIN 快閃記憶體中的 BSL 配置包含 GPIO 叫用的 PAD、接腳和極性定義。裝置由 TI 針對特定 GPIO 和極性進行配置,但軟體可在 NONMAIN 快閃記憶體的 BSL 配置中修改 GPIO 接腳配置,以變更此預設值。請參閱裝置特定產品規格表以判斷預設 BSL 叫用 GPIO。圖 10-1 顯示具高位準的 GPIO 接腳 PA18 觸發開機載入程式之範例。

圖 10-1 已配置 GPIO 接腳的 BSL 輸入順序

圖 10-1 已配置 GPIO 接腳的 BSL 輸入順序

圖 10-1 已配置 GPIO 接腳的 BSL 輸入順序

圖 10-1 已配置 GPIO 接腳的 BSL 輸入順序