NESA010A november 2022 – march 2023 MSPM0L1227 , MSPM0L1227-Q1 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L2227 , MSPM0L2227-Q1 , MSPM0L2228 , MSPM0L2228-Q1

9.2 接地佈線圖考量事項

系統接地是與電路板雜訊和 EMI 問題相關的最關鍵領域與基礎。將這些問題降到最低的最實際方法是使用單獨的接地平面。

什麼是接地雜訊?

每個從電路 (例如驅動器) 產生的訊號都有返回電流透過接地路徑流向其源極。隨着頻率的增加,或甚至是繼電器等簡單但電流高的開關,都會因線路阻抗在接地系統中產生干擾,而導致電壓下降。傳回路徑始終透過最小電阻。對 DC 訊號而言為最低電阻路徑,高頻訊號而言則是最低阻抗路徑。這說明接地平面可簡化問題,同時也是確保訊號完整性的關鍵。

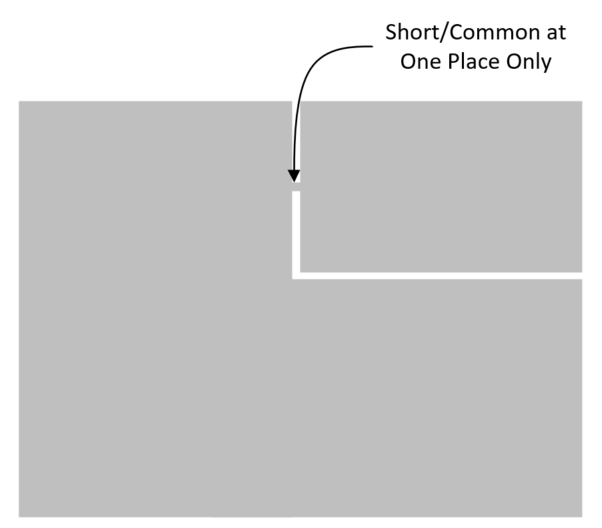

不建議數位傳回訊號傳播至類比傳回 (接地) 區域內;因此請將接地平面分割,讓所有數位訊號傳回迴圈保持在其接地區域內。請小心進行分割作業。許多設計採用單一 (共用) 電壓穩壓器來產生相同電壓位準的數位與類比供應 (例如 3.3 V)。隔離類比軌和數位電源軌及其各自的接地。隔離接地時請小心,因爲兩個接地都必須在某處短路。圖 9-2 說明為何不允許可能的數位訊號傳回路徑形成通過類比接地的迴路。在每個設計上,考慮零組件放置位置等以決定共同點。請勿在與接地軌跡的串聯中加入任何電感器 (鐵氧體磁珠) 或電阻 (零 Ω 也不可以)。阻抗會因高頻率下的相關電感而增加,進而造成電壓差動。請勿將參考數位接地的訊號透過類比接地或其他方向進行路由。

圖 9-2 數位與類比接地和共用區域

圖 9-2 數位與類比接地和共用區域