SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.1 Power Supply Layout

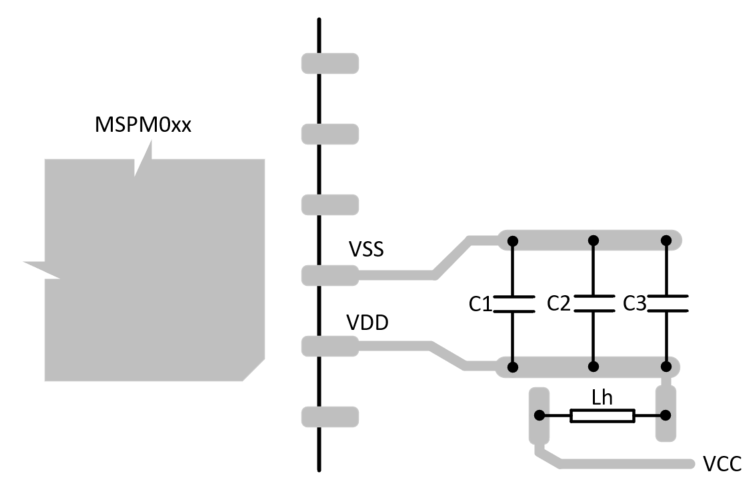

Figure 9-1 shows the typical parts placement and routing for the power supply layout; you must modify this appropriately for your MSPM0G part. You can optionally connect a filter inductor in series with the VCC and MCU VDD pins. This inductor is used to filter the switching noise frequency of DCDC. For the value, please refer to the data sheet of DCDC vendor. C1/C2/C3 values and layout in the MSPM0G device data sheets.

Note:

- Keep the smallest capacitance, closest to the MCU VDD pin (C1 < C2 < C3).

- Make all the traces direct without any vias.

Figure 9-1 Suggested Power Supply Layout

Figure 9-1 Suggested Power Supply Layout