SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

6.3 DAC Design Considerations

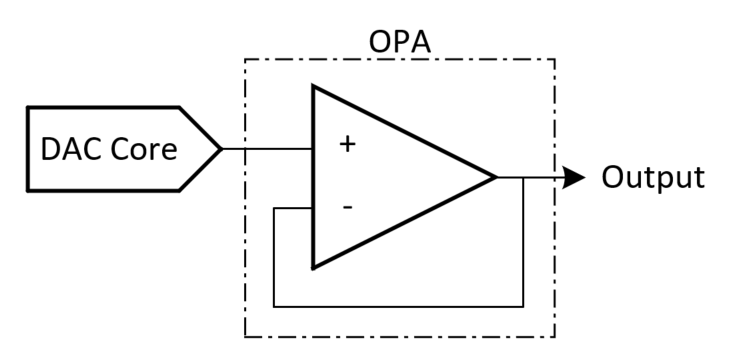

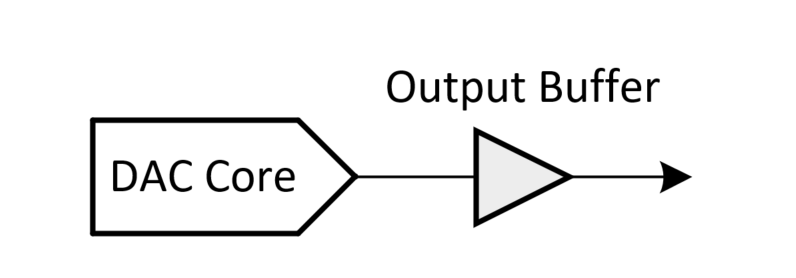

MSPM0G devices include two DAC modules: 8-bit and 12-bit. The DAC can be used as the reference voltage and also can work with the OPA to drive the output pad directly. 12-bit DAC modules include a buffer, thus this can output to pad directly. However, the 8-bit DAC module is normally used as internal reference voltage for OPA and COMP, therefore to output to an external pin, the OPA must be configured into buffer mode to improve the drive strength.

Not all devices include these two DAC modules. See the device-specific data sheet for details.

Figure 6-4 8-Bit DAC Block Diagram

Figure 6-4 8-Bit DAC Block Diagram Figure 6-5 8-Bit DAC and OPA Output Block Diagram

Figure 6-5 8-Bit DAC and OPA Output Block Diagram Figure 6-6 12-bit DAC Output Block Diagram

Figure 6-6 12-bit DAC Output Block Diagram