SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

10.2.2 Hardware Invocation

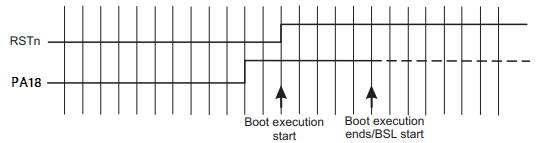

The bootloader supports hardware invocation after a BOOTRST through the use of a GPIO. The BSL configuration in the NONMAIN flash memory contains the pad, pin, and polarity definition for the GPIO invocation. Devices come configured from TI for a specific GPIO and polarity, but software can change this default by modifying the GPIO pin configuration in the BSL configuration in NONMAIN flash memory. See the device specific data sheet to determine the default BSL invoke GPIO. Figure 10-1 shows an example for the GPIO pin PA18 with high level to trigger bootloader.

Figure 10-1 BSL Entry Sequence at Configured GPIO Pin

Figure 10-1 BSL Entry Sequence at Configured GPIO Pin