SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

4.4 Frequency Clock Counter (FCC)

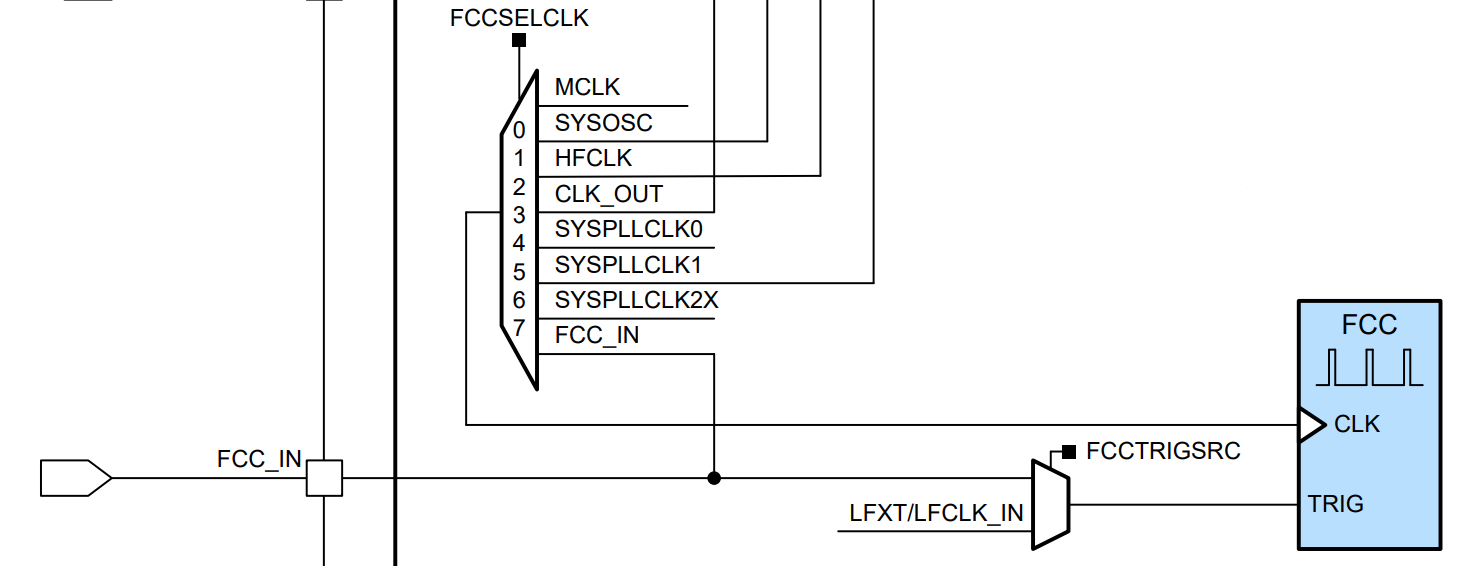

The frequency clock counter (FCC) enables flexible in-system testing and calibration of a variety of oscillators and clocks on the device. The FCC counts the number of clock periods seen on the selected source clock within a known fixed trigger period (derived from a secondary reference source) to provide an estimation of the frequency of the source clock.

Figure 4-7 MSPM0G Frequency Clock Counter

Block Diagram

Figure 4-7 MSPM0G Frequency Clock Counter

Block DiagramApplication software can use the FCC to measure the frequency of the following oscillators and clocks:

- MCLK

- SYSOSC

- HFCLK

- CLK_OUT

- SYSPLLCLK0

- SYSPLLCLK1

- SYSPLLCLK2X

- The external FCC input (FCC_IN)