SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

2.3 Built-in Power Supply and Voltage Reference

The VREF module for the MSPM0G family is a shared voltage reference module that can be leveraged by a variety on on-board analog peripherals.

The VREF module features include:

- 1.4-V and 2.5-V user-selectable internal references.

- Support for receiving external reference on the VREF+ and VREF- device pins.

- Sample and hold mode support VREF operation down to STANDBY operating mode.

- Internal reference supports for ADC, COMP, and OPA.

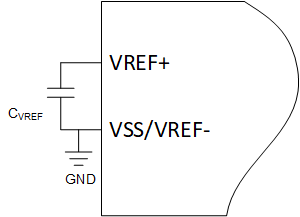

When supplying the MCU with an external reference, TI recommends connecting a decoupling capacitor on the reference pins with a value based on the voltage source (see Figure 2-2).

Figure 2-2 VREF Circuit

Figure 2-2 VREF Circuit