SLAAE76B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

6.5 GPAMP Design Considerations

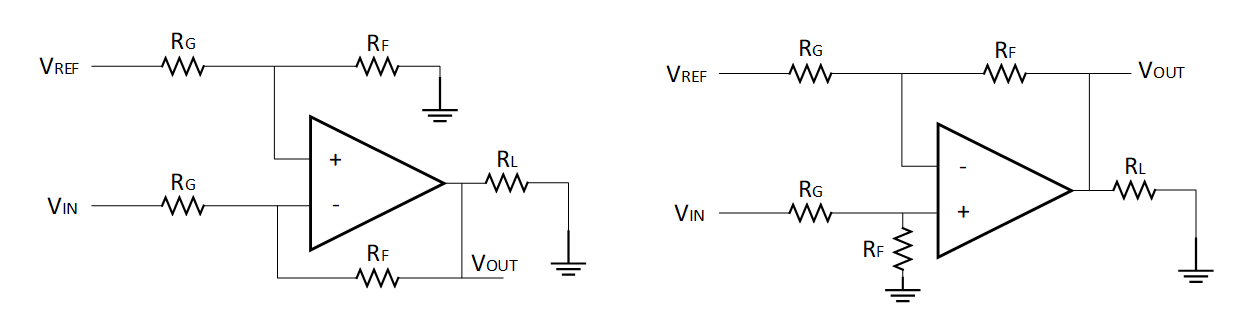

MSPM0G devices includes GPAMP (General Purpose Amplifier) modules that can used for signal amplification with some external resistors and capacitors, as seen in Figure 6-10.

Figure 6-10 GPAMP Circuit in Amplify

Mode

Figure 6-10 GPAMP Circuit in Amplify

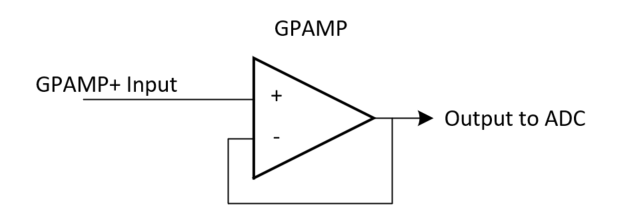

ModeThe GPAMP can also be used as a buffer for the internal ADC. Figure 6-11 shows an example of this configuration.

Figure 6-11 GPAMP Circuit in Buffer Mode

Figure 6-11 GPAMP Circuit in Buffer Mode