SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

4.2.1 LFCLK_IN

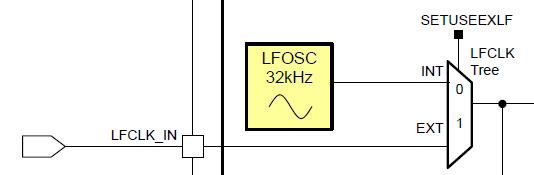

To configure LFCLK to use a digital clock input, first configure the IOMUX to enable the LFCLK_IN function on the appropriate pin. When IOMUX is configured correctly and the external clock source is outputting a 32 kHz clock to LFCLK_IN, set the SETUSEEXLF bit in the EXLFCTL register in SYSCTL.

LFCLK_IN is compatible with digital square wave CMOS clock inputs and a typical duty cycle of 50% is recommanded. Check for a valid clock signal on LFCLK_IN by enabling the LFCLK monitor before setting SETUSEEXLF in the EXLFCTL register is recommanded. By default, the LFCLK monitor will check LFCLK_IN if the LFXT was not started.

Once LFCLK_IN is selected as the LFCLK source, change back to LFOSC or LFXT without going through a BOOTRST is not possible.

Figure 4-2 MSPM0C Series External Clock Input LFCLK_IN

Figure 4-2 MSPM0C Series External Clock Input LFCLK_IN