SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

1 MSPM0C Hardware Design Check List

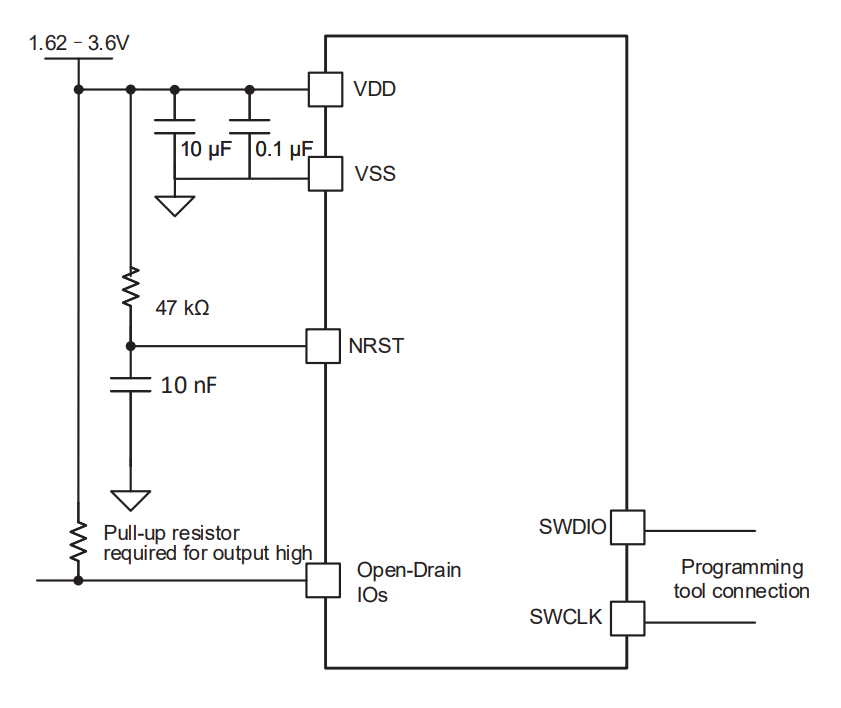

Table 1-1 describes the main signal that needs to be checked during the MSPM0C hardware design process. The following sections provide more details.

| Pin (1) | Description | Requirements |

|---|---|---|

| VDD | Power supply positive pin | Place 10-µF and 100-nF capacitors between VDD and VSS, and keep those part close to VDD and VSS. |

| VSS | Power supply negative pin | |

| NRST | Reset pin | Connect an external 47-kΩ pullup resistor with a 10-nF pulldown capacitor. |

| SWCLK | Serial wire clock from debug probe | Internal pulldown to VDD, does not need any external part. |

| SWDIO | Bidirectional (shared) serial wire data | Internal pullup to VSS, does not need any external part. |

| PA0, PA1 | Open-drain I/O | Pull-up resistor required for output high |

| PAx (exclude PA0, PA1) | General-purpose I/O | Set corresponding pin functions to GPIO (PINCMx.PF = 0x1) and configure unused pins to output low or input with internal pullup or pulldown resistor. |

TI recommends connecting a combination of a 10-μF and a 0.1-nF low-ESR ceramic decoupling capacitor to the VDD and VSS pins. Higher-value capacitors can be used but can impact supply rail ramp-up time. Decoupling capacitors must be placed as close as possible to the decoupled pins (within a few millimeters).

The NRST reset pin is required to connect an external 47-kΩ pullup resistor with a 10-nF pulldown capacitor.

For 5-V-tolerant open drain (ODIO), a pullup resistor is required to output high, this is required for inter-integrated circuit (I2C) and universal asynchronous receiver/transmitter (UART) functions if the ODIO are used.

Figure 1-1 MSPM0C Typical Application

Schematic

Figure 1-1 MSPM0C Typical Application

Schematic