SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

6.1 ADC Design Considerations

MSPM0C devices have a 12-bit, up to 1.5-Msps, analog-to-digital converter (ADC). The ADC supports fast 12-, 10-, and 8-bit analog-to-digital conversions. The ADC implements a 12-bit SAR core, sample/conversion mode control, and up to 4 independent conversion-and-control buffers.

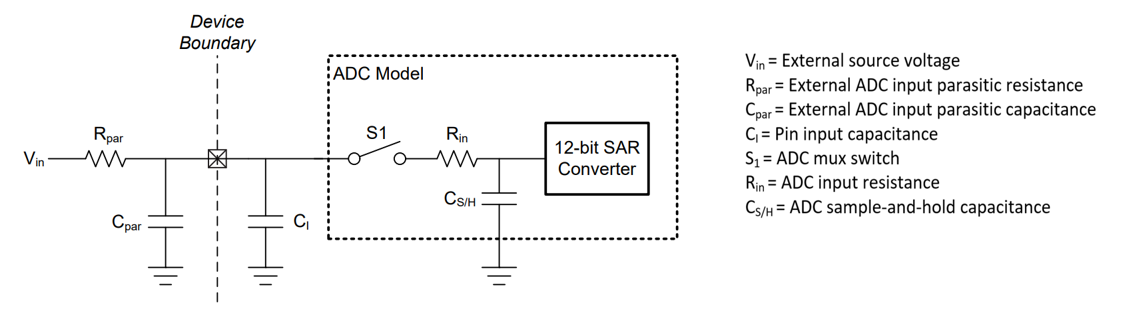

Figure 6-1 ADC Input Network

Figure 6-1 ADC Input NetworkTo achieve the desired conversion speed and keep high accuracy, set the proper sampling time in the hardware design. Sampling (sample-and-hold) time determines how long to sample a signal before digital conversion. During sample time, an internal switch lets the input capacitor charge. The required time to fully charge the capacitor is dependent on the external analog front-end (AFE) connected to the ADC input pin. Figure 6-1 shows a typical ADC model of an MSPM0C MCU. The Rin and CS/H values can be obtained from the device-specific data sheet. It is critical to understand the AFE drive capability and calculate the minimum sampling time required to sample the signal. The resistance of Rpar and Rin affects tsample. Equation 1 can be used to calculate a conservative value of the minimum sample time tsample for an n-bit and fixed settling error conversion: