SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

3.1 Digital Power Supply

The device has five reset levels:

- Power-on reset (POR)

- Brown-out reset (BOR)

- Boot reset (BOOTRST)

- System reset (SYSRST)

- CPU reset (CPURST)

The details of the relationships between reset levels is described in the MSPM0 C-Series 24-MHz Microcontrollers Technical Reference Manual.

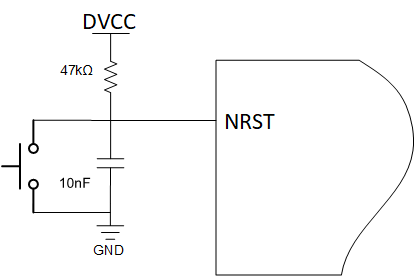

After a cold start, the NRST pin is configured in NRST mode. The NRST pin must be high for the device to boot successfully. There is no internal pullup resistor on NRST. External circuitry (either a pullup resistor to DVCC or a reset control circuit) must actively pull NRST high for the device to start. A capacitor and an open button are needed for manual reset (see Figure 3-1). After the device is started, a low pulse on NRST that is <1 second in duration triggers a BOOTRST. If a low pulse on NRST is held for >1 second, a POR is triggered.

Figure 3-1 NRST Recommended Circuit

Figure 3-1 NRST Recommended Circuit