SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

4.4 Frequency Clock Counter (FCC)

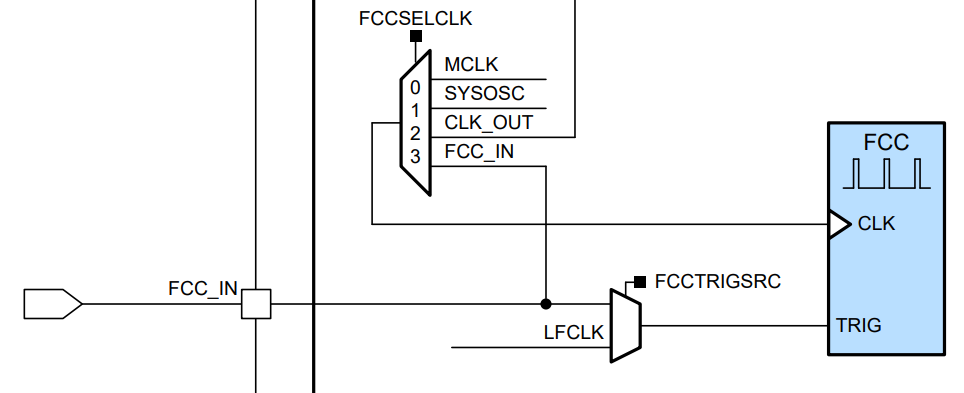

The frequency clock counter (FCC) enables flexible in-system testing and calibration of a variety of oscillators and clocks on the device. The FCC counts the number of clock periods seen on the selected source clock within a known fixed trigger period (derived from a secondary reference source) to provide an estimation of the frequency of the source clock.

Figure 4-5 MSPM0C Series Frequency Clock Counter Block Diagram

Figure 4-5 MSPM0C Series Frequency Clock Counter Block DiagramApplication software can use the FCC to measure the frequency of the following oscillators and clocks:

- MCLK

- SYSOSC

- CLK_OUT

- The external FCC input (FCC_IN)

Note: While the external FCC input (FCC_IN function) can be used as either the FCC clock source or the FCC trigger input, it cannot be used for both functions during the same FCC capture. It must be configured as either the FCC clock source or the FCC trigger.