SLAAEG4 October 2023 MSPM0C1104 , MSPM0L1306

9.4 How to Select Board Layers and Recommended Stack-up

To reduce the reflections on high speed signals, it is necessary to match the impedance between the source, sink and transmission lines. The impedance of a signal trace depends on its geometry and its position with respect to any reference planes.

The trace width and spacing between differential pairs for a specific impedance requirement is dependent on the chosen PCB stack-up. As there are limitations in the minimum trace width and spacing which depend on the type of PCB technology and cost requirements, a PCB stack-up needs to be chosen which allows all the required impedances to be realized.

The minimum configuration that can be used is 2 stack-up. A 4- or 6-layer boards is required for very dense PCBs that have multiple high-speed signals.

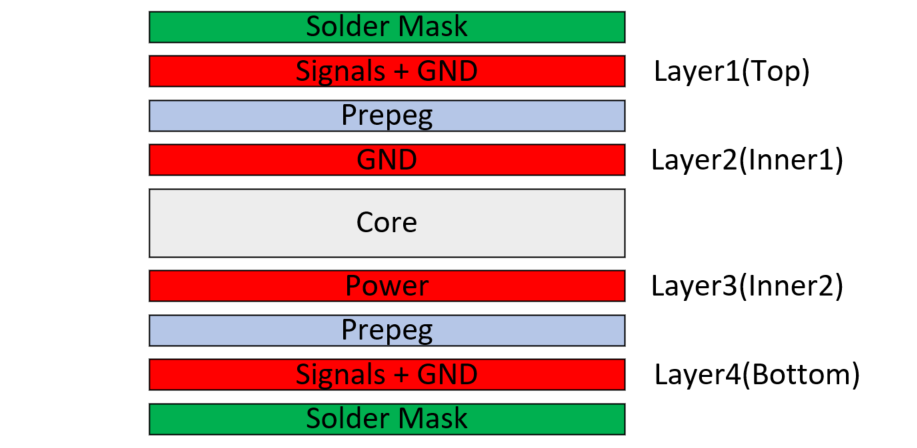

The following stack-up (see Figure 9-5) is a 4-layer examples that can be used as a starting point for helping in a stack-up evaluation and selection. These stack-up configurations are using a GND plane adjacent to the power plane to increase the capacitance and reduce the gap between GND and power plane. So high speed signals on top layer will have a solid GND reference plane which helps to reduce EMC emissions, as going up in number of layers and having a GND reference for each PCB signal layer will improve further the radiated EMC performance.

Figure 9-5 Four-Layer PCB Stack-up

Example

Figure 9-5 Four-Layer PCB Stack-up

ExampleIf the system is not very complicated, there is no high-speed signal or some sensitive analog signal, then the 2 stack-up structure is sufficient.